Hi dear supporting team,

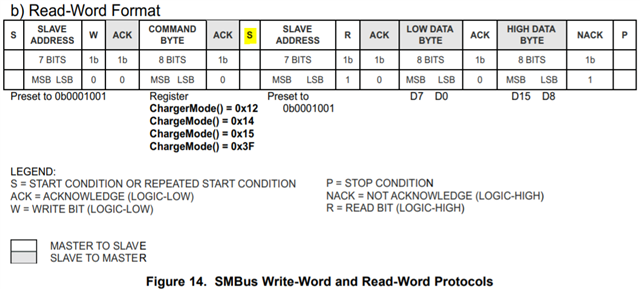

When reading the registers of Battery Charger SMBus Registers, I think that it is done as follows.

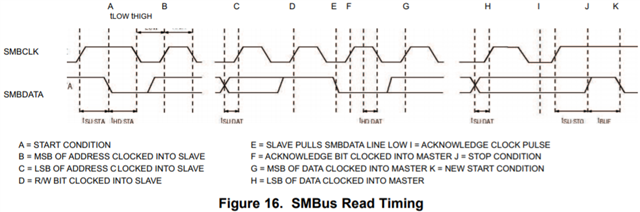

(1)Start condition

(2)Send SLAVE ADDRESS (0b0001001) +0b0 in sync with CLK from the master device

(3)ACK returned from BQ24765 during ninth clock

(4)Send COMMAND BYTE(8bit) from master device

(5)ACK returned from BQ24765 during ninth clock

(6)Send SLAVE ADDRESS (0b0001001) +0b1 in sync with CLK from the master device

(7)ACK returned from BQ24765 during ninth clock

(8)LOW BYTE DATA are output from BQ24765 in synchronization with CLK

(9)ACK returned from master device during ninth clock

(10)HIGH BYTE DATA are output from BQ24765 in synchronization with CLK

(11)NACK returned from master device during ninth clock

(12)Stop condition

Do I need wait time between (7) and (8) ?