Hi team,

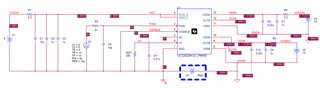

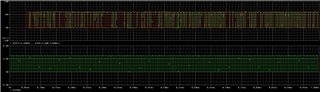

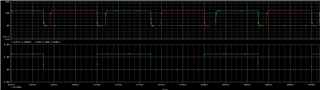

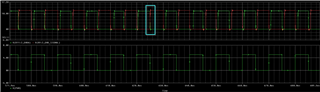

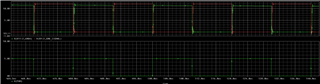

We are trying to run Spice simulations using the PSpice for TI tool in order to analyze the UCC20225A behavior. Nevertheless, it seems that the Dead Time (DT) implemented in the model is not working, as the two output signals (OUTA and OUTB) are overlapped, regardless of the resistor value connected on the DT pin. Please, find attached two images. Thank you in advance.

Best regards,