Hi

We are facing some problems with our multi phase converter using UCD9224 and UCD74111. Please answer my queries below:

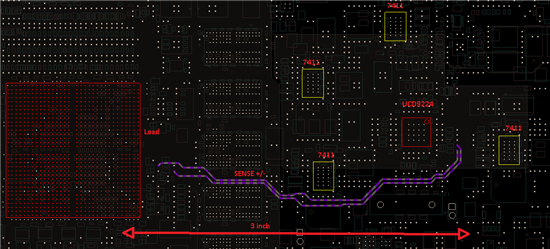

The specs of the converter are : . 12V to 1V @ 48 A (SoC requires only 40A), 4 phases at switching frequency of 700KHz, c. No phase shedding at low loads,. Current sensed using 2mOhm sense resistor, 1V Enabled using the the seq1 pin (Active High) and stay on dependency also on seq1 pin (Active High)

configuration file : Attached

The issues are:

- Problem we are facing is that the Seq1 input is not responding to every other pulse, so we have to toggle the seq1 pin two times to get the rail On. Note that the first time after each power on the rail turns on when seq1 goes high. Once the rail is ON , then if you want to power cycle the rail you need to apply two pulses. (The power supply is configured to turn on when pin 21 (SEQ 1) is high. We have set the Turn on dependency and Stay on dependency as Pin 21 (Active High ) . Why does the seq1 pin behave so?

- We found that the rail sometimes switch off abruptly (although currently the rail is not even loaded to 5% ). It reports a MFR fault , and in the status page it shows a FLT fault. We checked the FLT pins after rail went down, FLT o/ps of all UCD74111 were low. What could be the possible casue for a FLT fault. Also please let me know where can I find the description of each error mentioned in the status page of the Fusion designer?

- Although we don’t know the cause for abrupt FLT faults. We noticed that this FLT fault can be triggered by switching off the SEQ1 pin. Is that expected? We think the Seq1 input is stable even when the above mentioned abrupt FLT faults were observed

Thank You

Ashok