Other Parts Discussed in Thread: , TLV431B

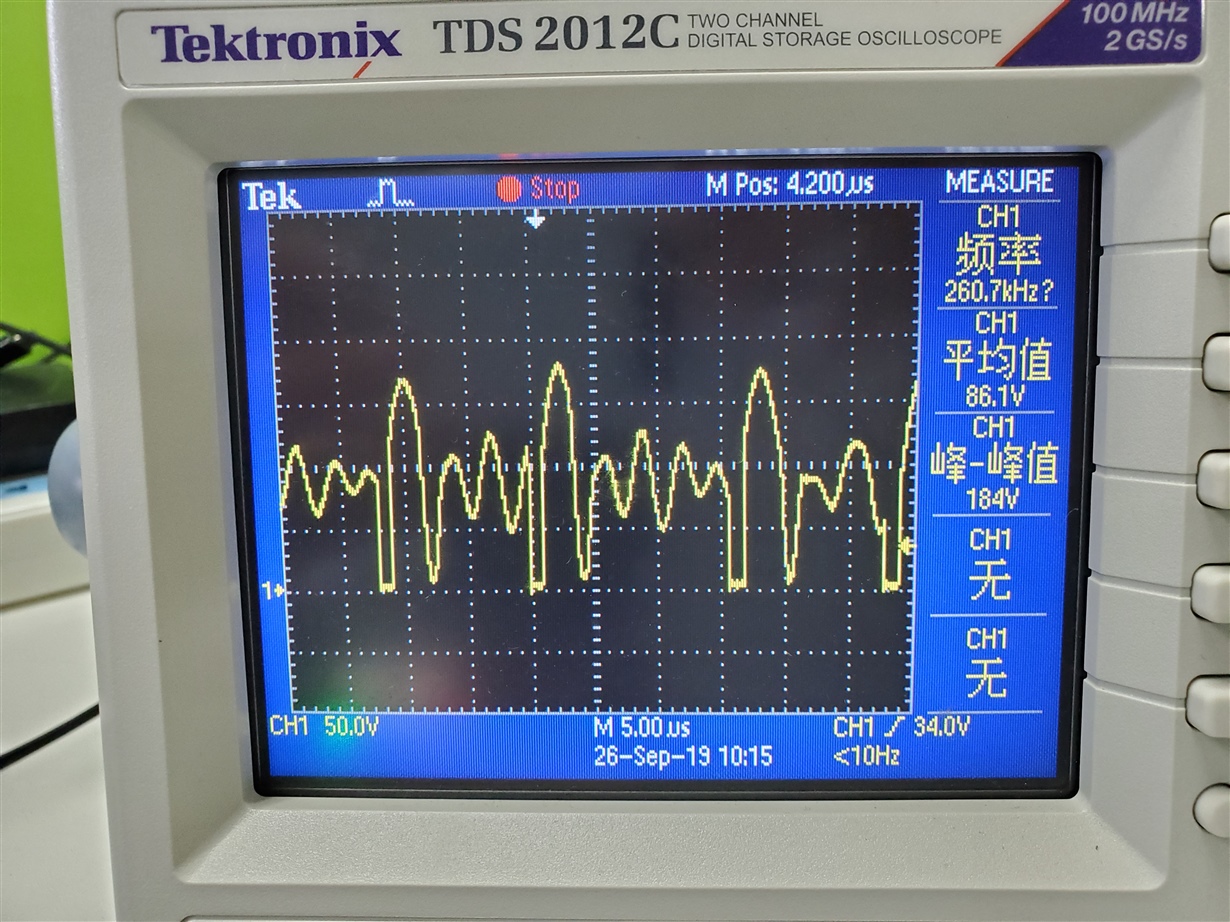

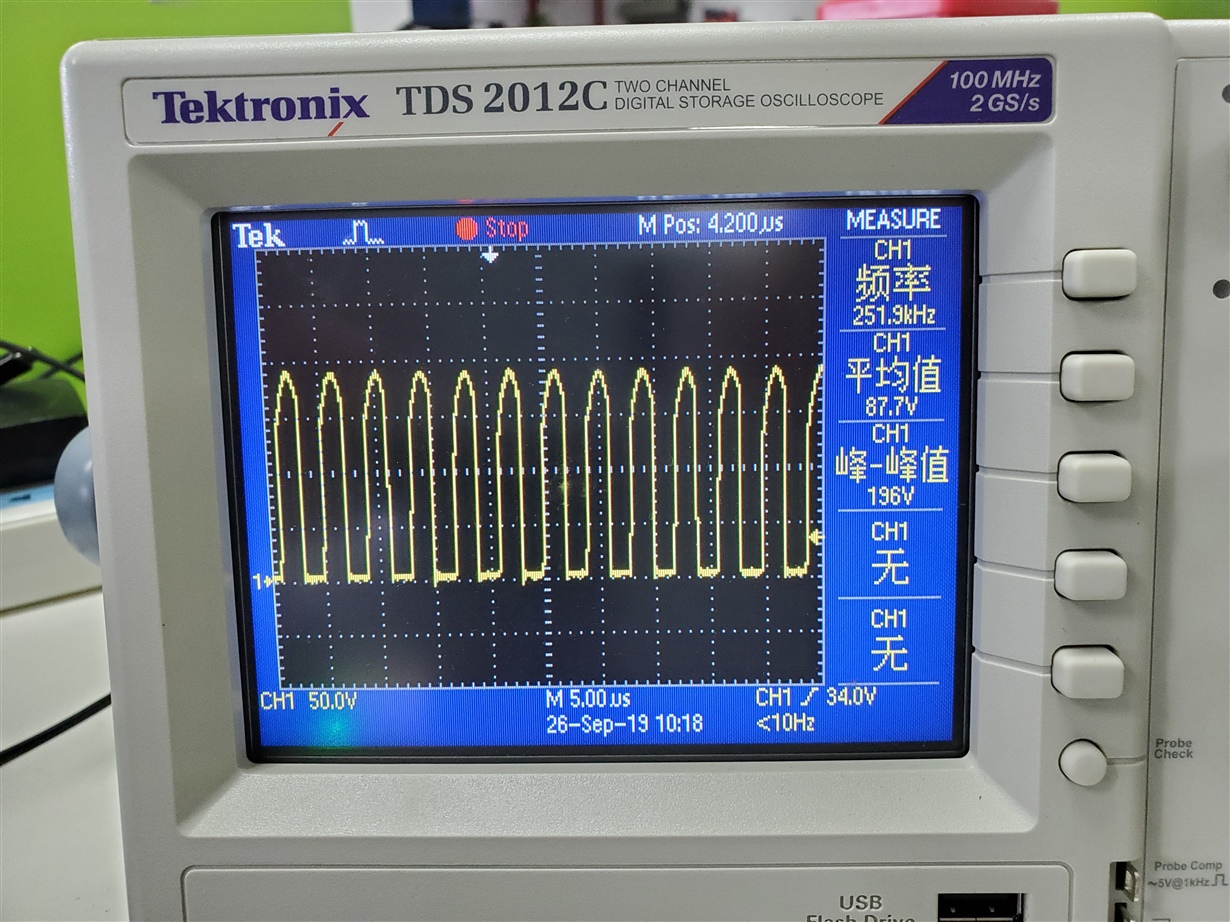

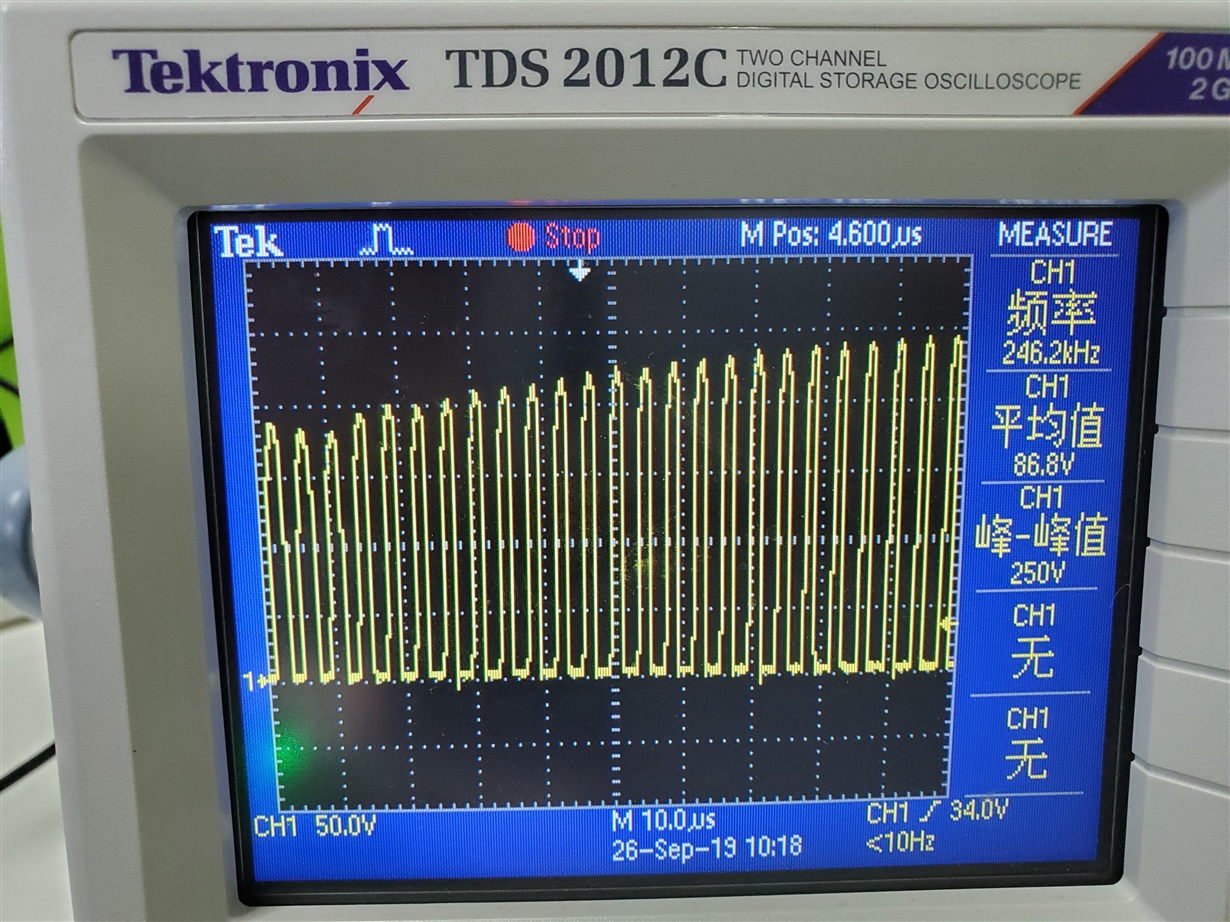

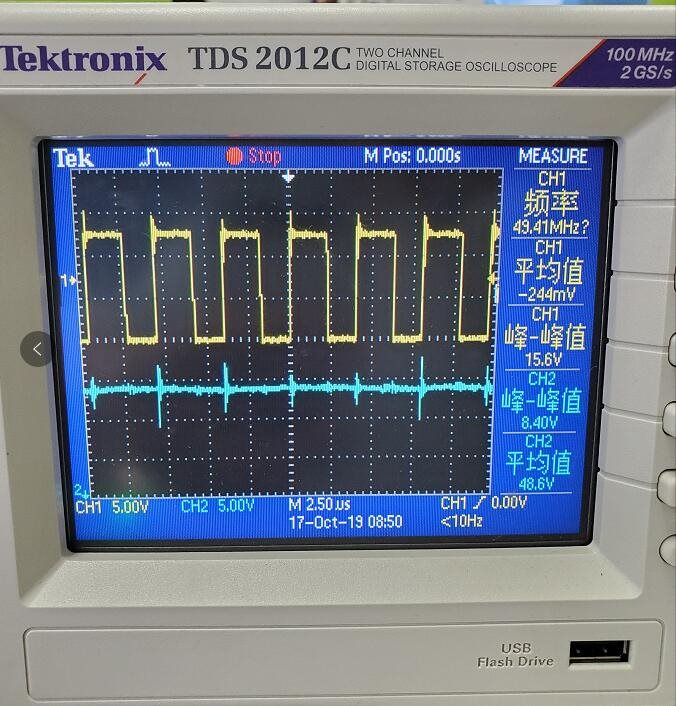

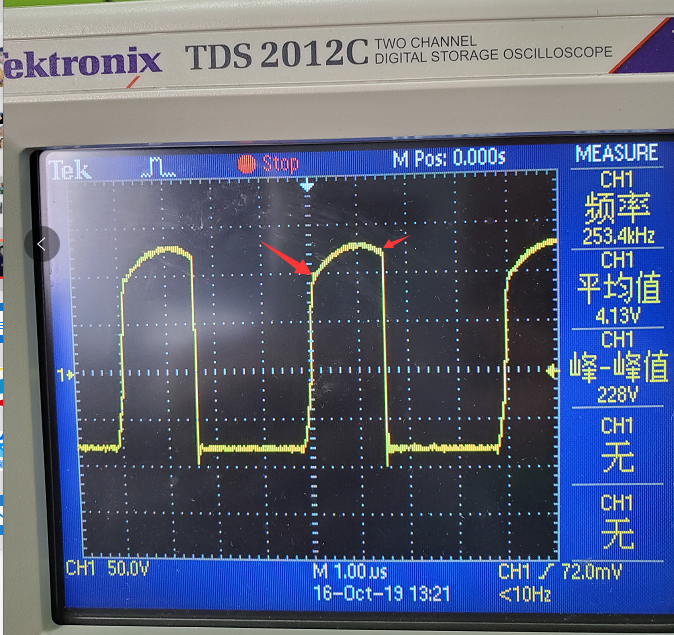

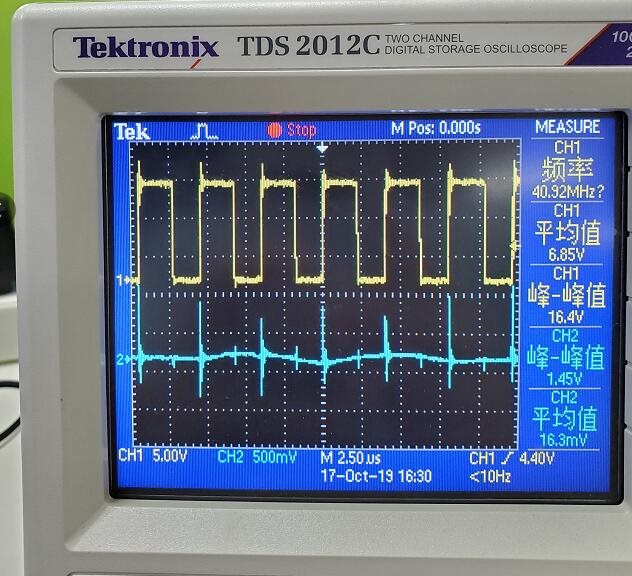

I recently had a project that used active clamp forward excitation topology with 66-160vdc input and 48v@3A output.The schematic diagram is attached.Currently it can output 48V, but not with load.FB is about 2.1v when no load, and 5V when light load, and the output voltage will be slightly reduced, increase the load voltage drop more severe, FB is still 5V.

When I adjust the feedback circuit, FB is about 3V when there is no load, and the voltage will rise to about 100V when the power is on.I want you to help me analyze the reason. Personally, I think the parameters of the feedback circuit are not set well.But I tried for a long time and still no result.

In addition, I want to know the Compensating the Feedback Loop parameters how to calculate?