Other Parts Discussed in Thread: TPS544B25, TPS543B20, TPS56221, TPS548B22

In the this thread i have got my PMIC schematic for MPSOC reviewed, imporatantly TPS650864 is used in this schematic for 0.72 core voltage generation

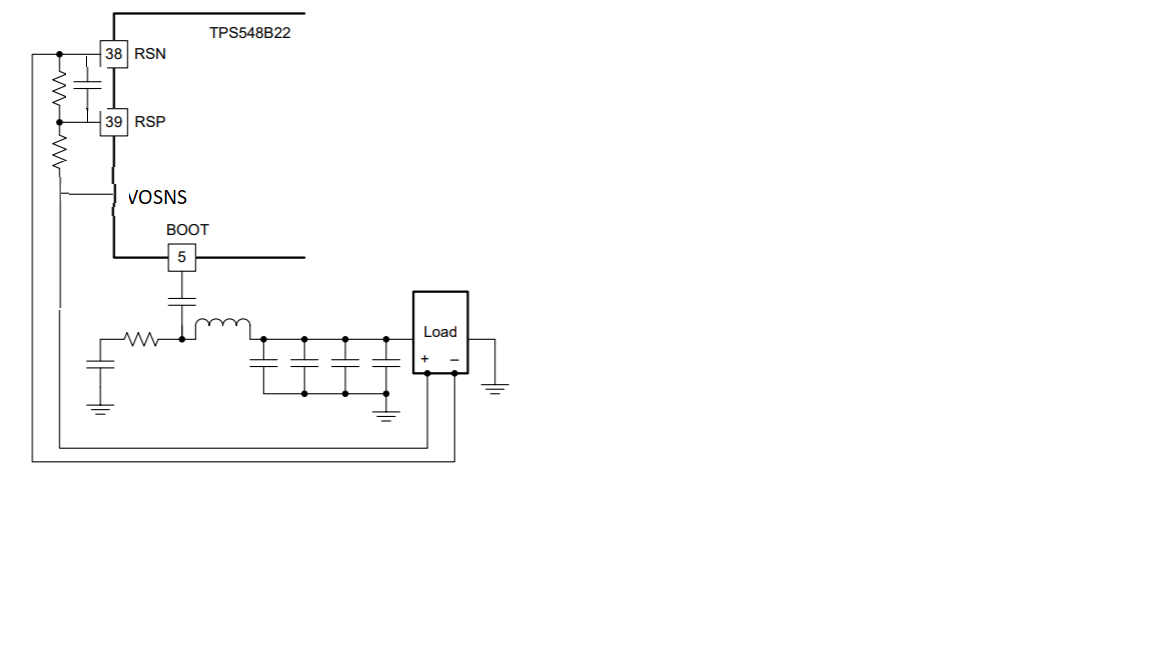

I have attached the reference that i generated from WEBENCH tool, i have tried to straight away use the design provided by WEBENCH, still i would like to take your second opinion

8004.SCHEMATIC_PMIC_MPSOC_XCZU6CG.pdf

Kindly review