Hello,

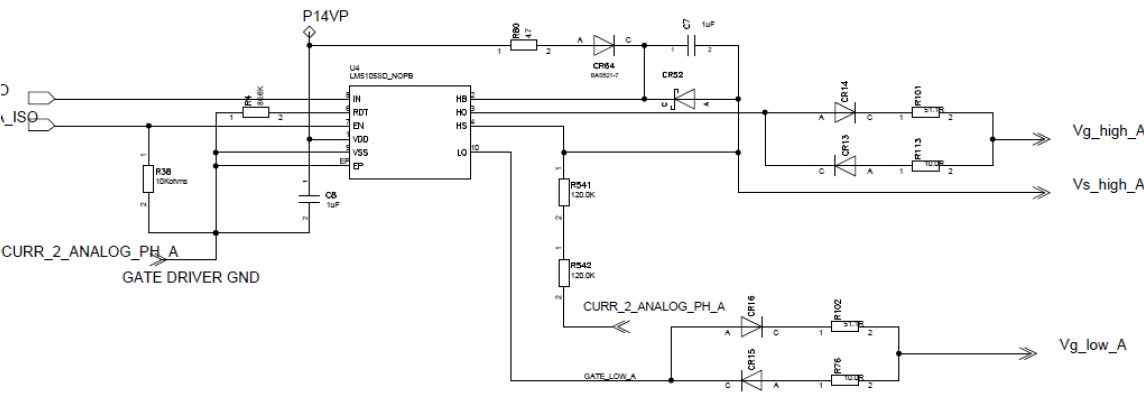

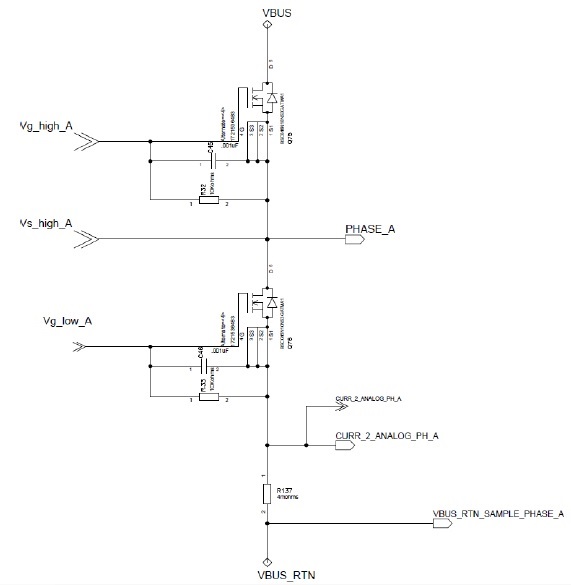

I'm using LM5105SD gate driver for implementing 3 phase H-bridge motor driver, I'm using BSC046N10NS Infineon FET, the PWM frequency is 18kHz.

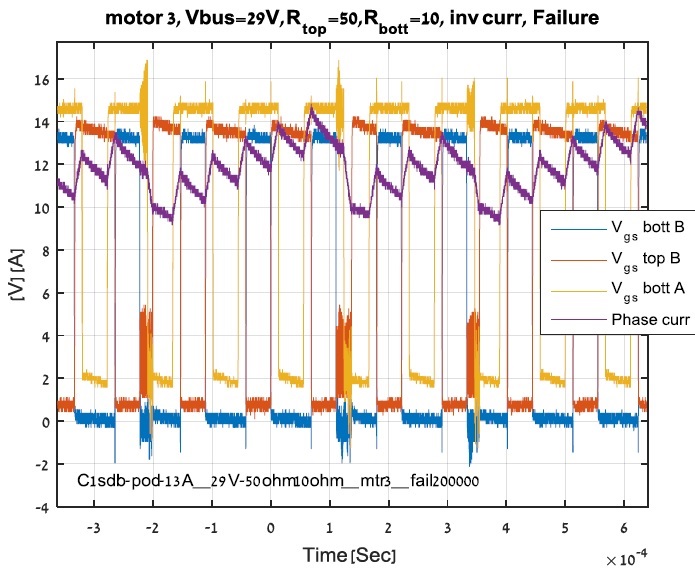

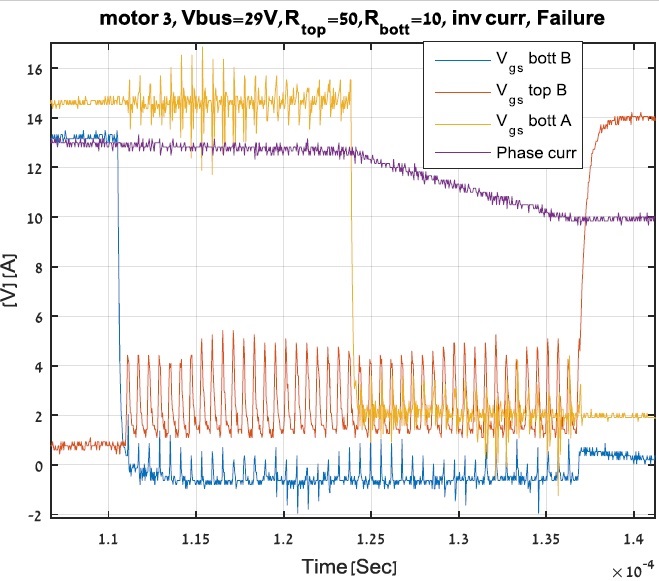

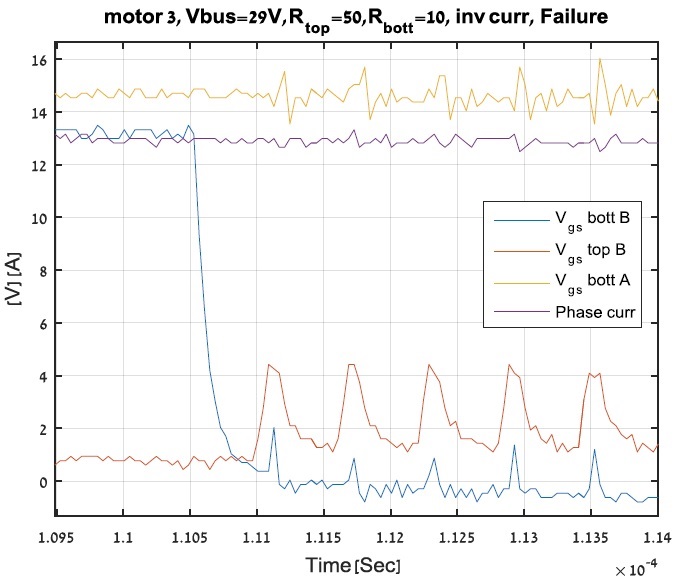

during activation of the circuit, i experienced upper FETs burns out. In the failure investigation i detected an unexplained phenomenon that the upper FET instead of start opening as expected (Vgs starts to rise) but the Vgs of the upper FET start to oscillate as well as both the Vgs of the lower FET and the other H-bridge FET's Vgs.

I attach the circuit diagram as well as recordings of both the upper and lower FET's Vgs and another phase lower FET's Vgs.

I'll be happy to receive comments on the circuit and help finding the source of the fault.

thanks, Rami.