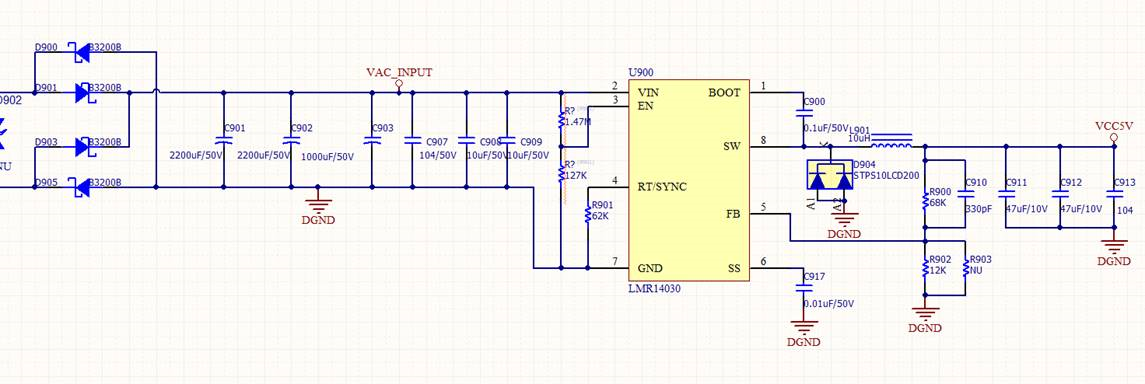

Other Parts Discussed in Thread: LMR14030

We found that the output voltage is abnormal during power off when LMR16030 is used. however, when p2p device of the LMR14030 is used, there is no problem during power off. Could you help to check if there is something missing on schematic! Especially, please check if the divider resistor for the EN pin control is ok or not?

Remark: In the customer design, there is a large capacitance of the 5500uF for the input ripple of the Full-waveform rectifier.

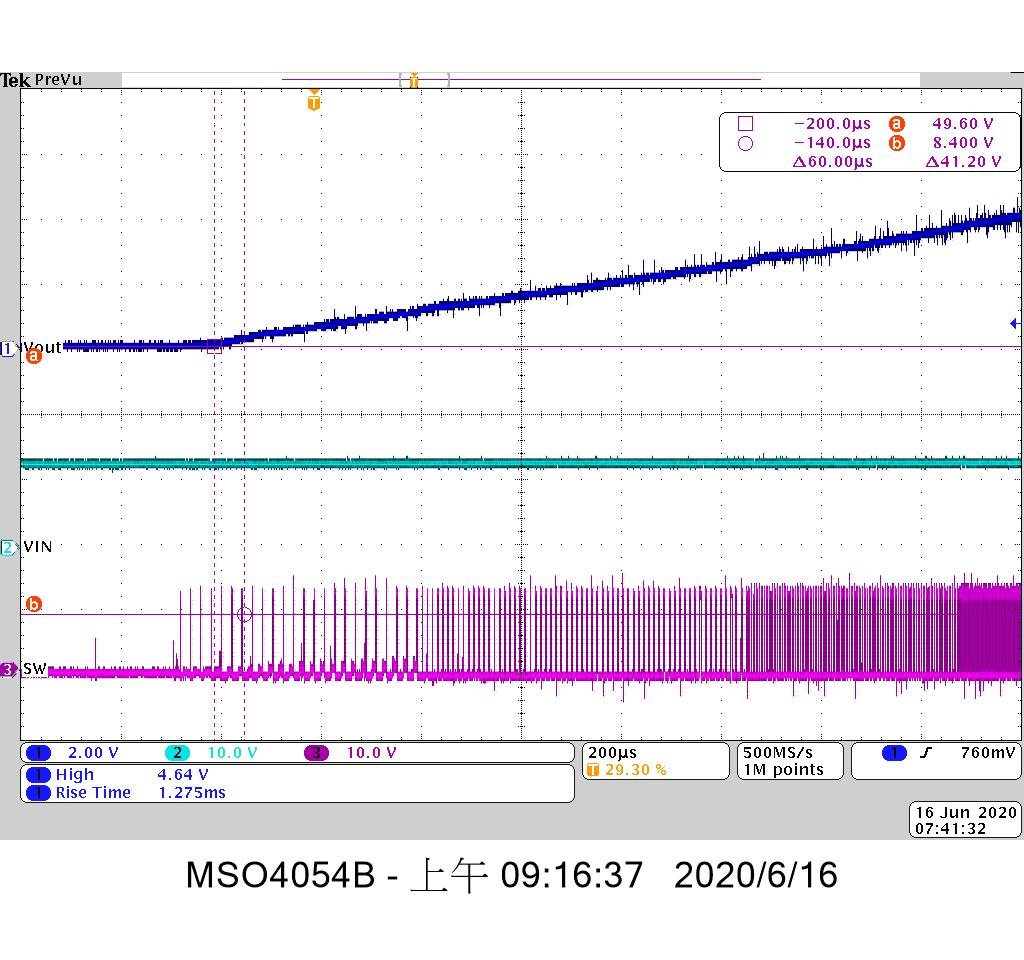

Condition: Vin:24V, Vout:5V, Iout:1.5A

***The schematic is following up the WEBENCH design.

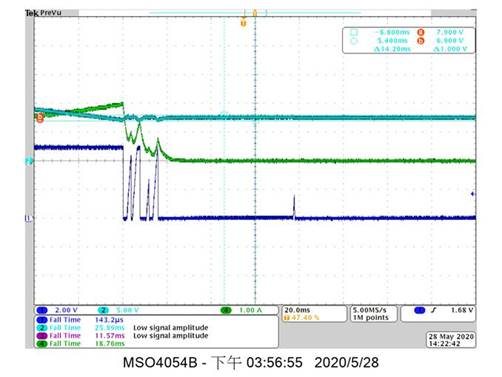

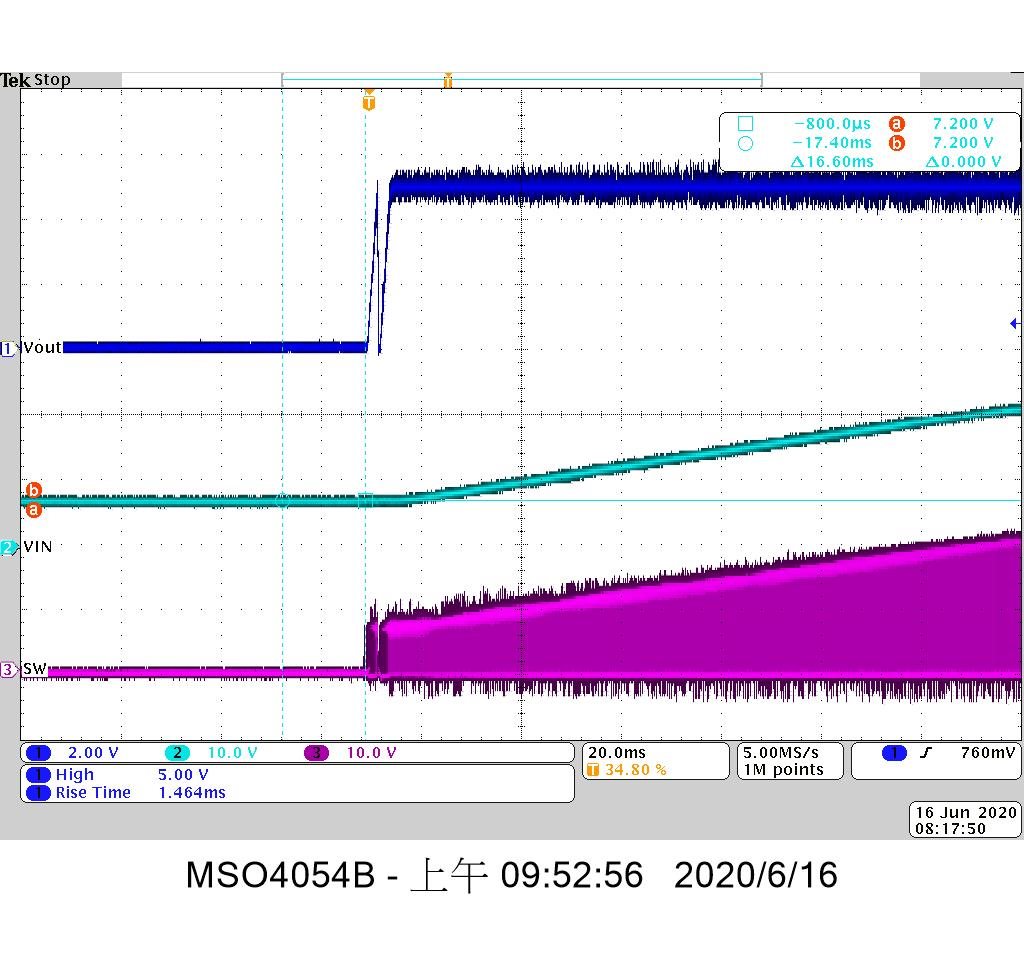

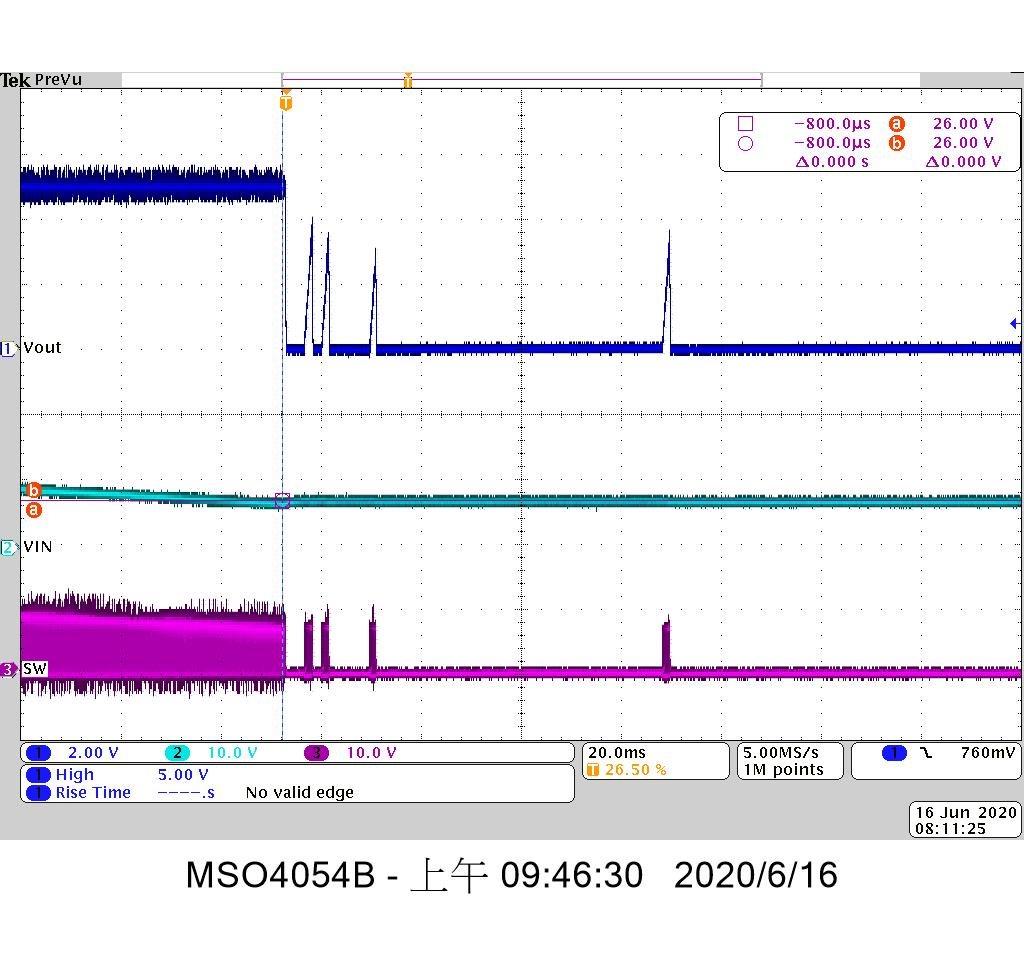

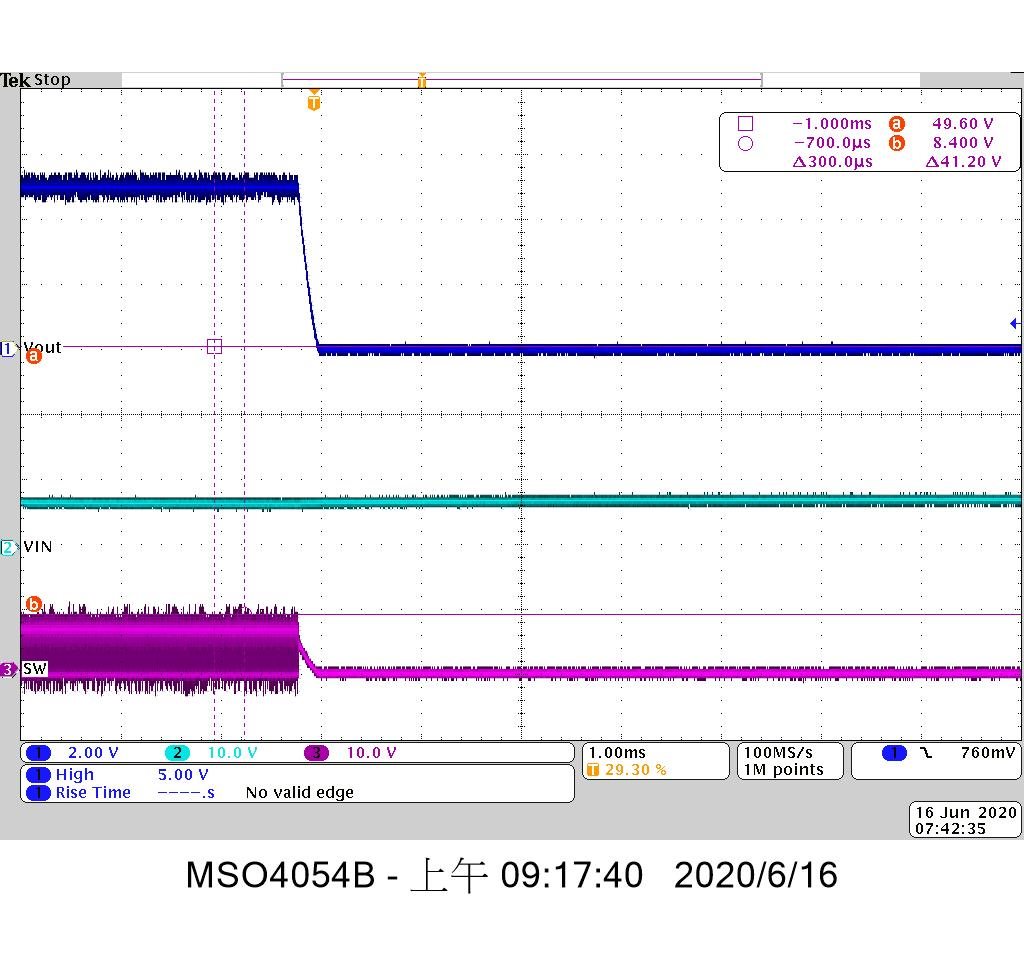

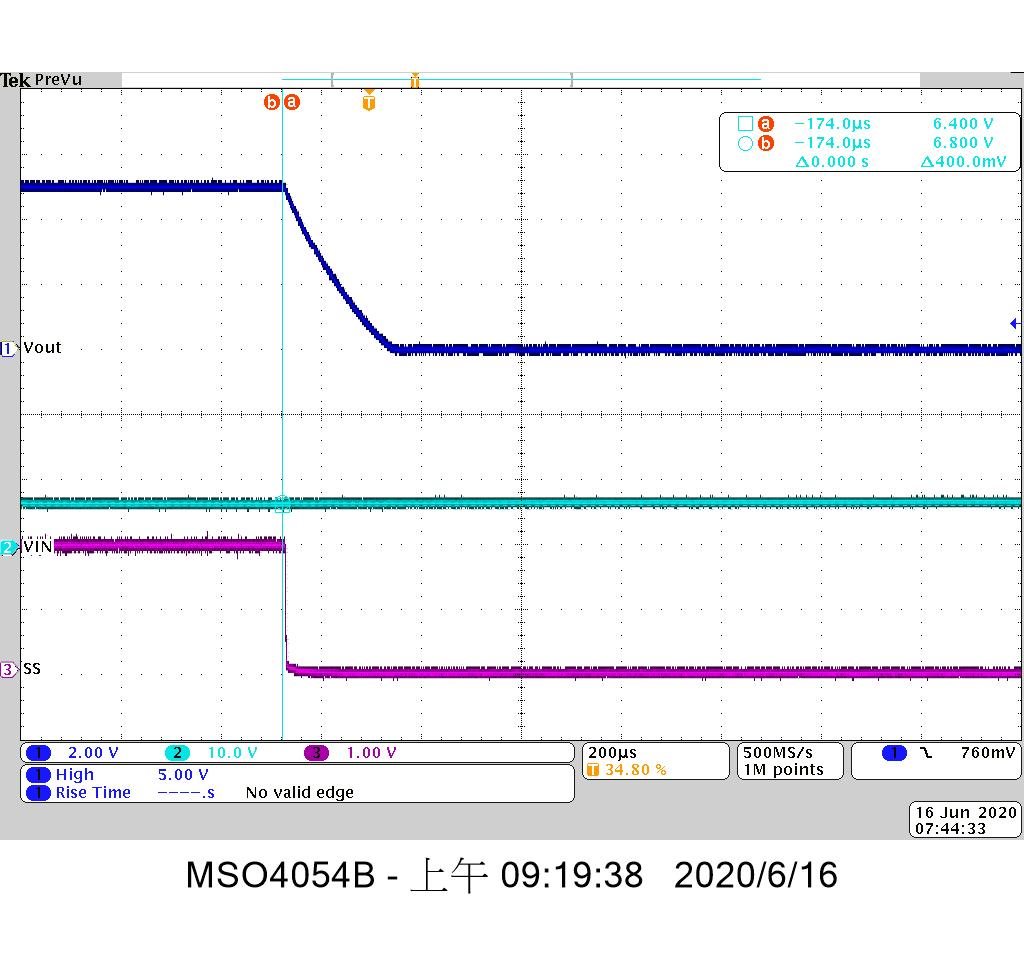

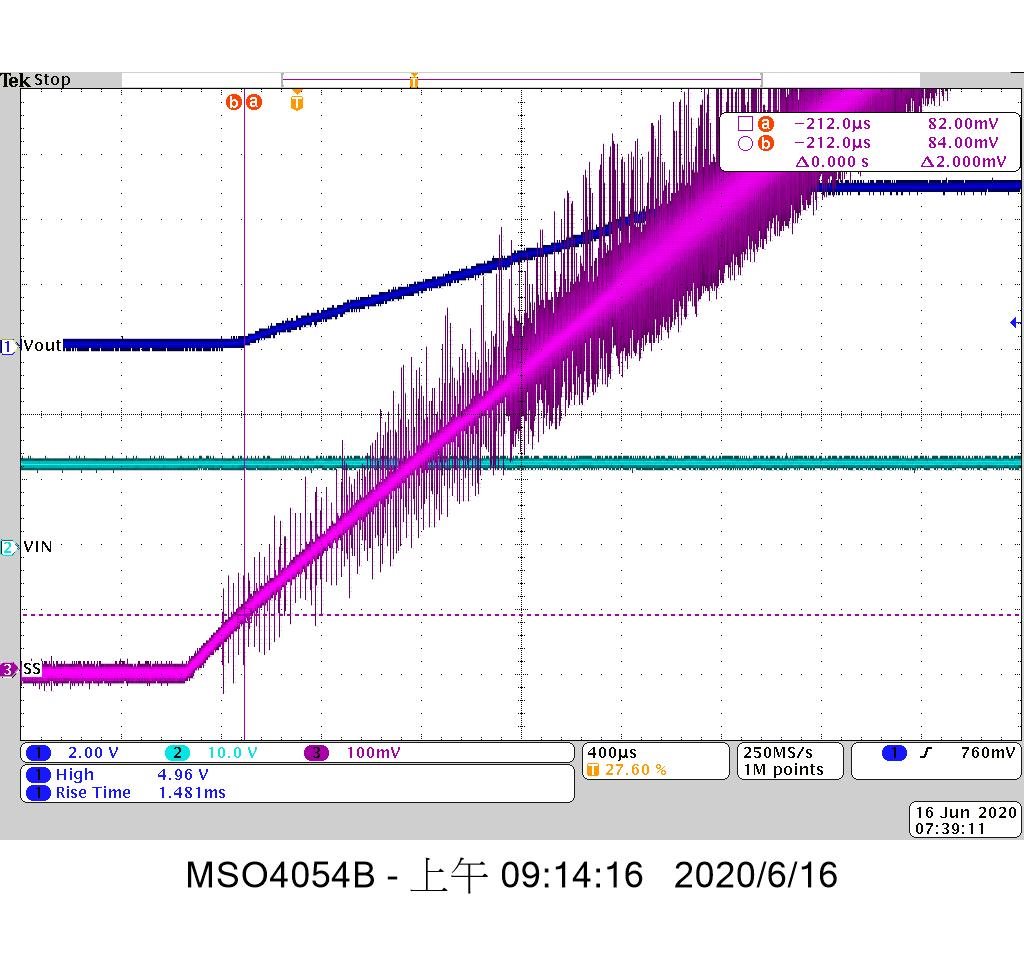

1. Test Result with LMR16030: CH1 VOUT 5V, CH2 VIN 24V, CH4 Input Current

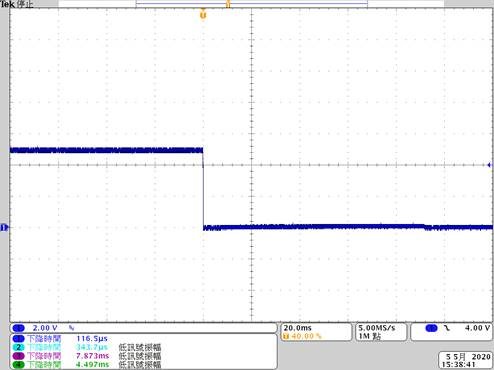

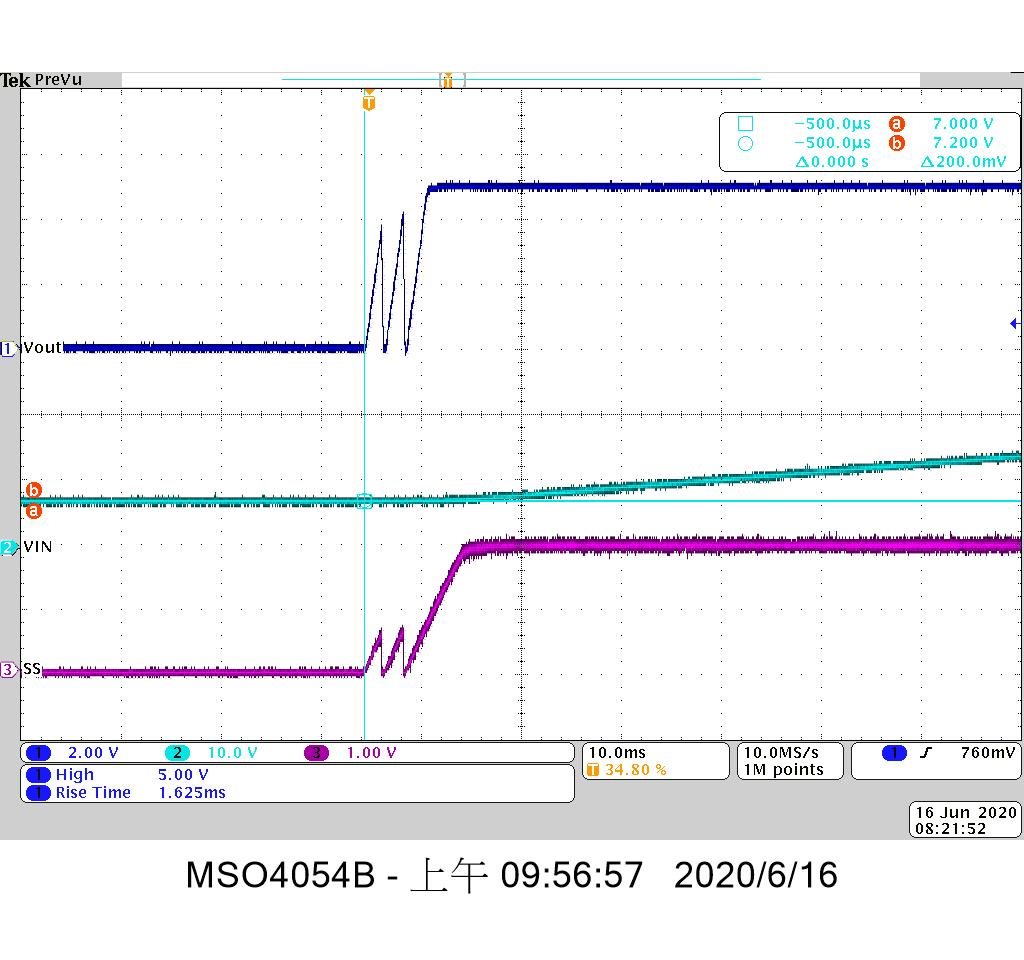

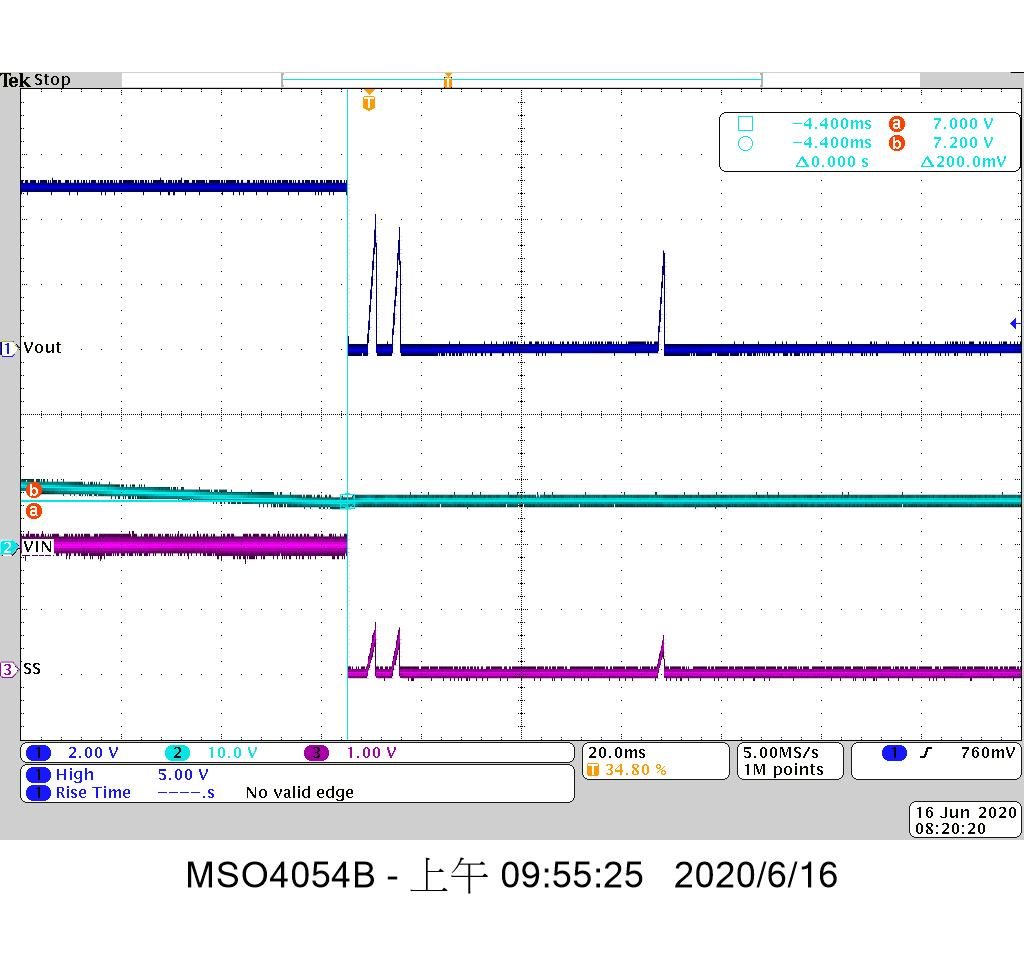

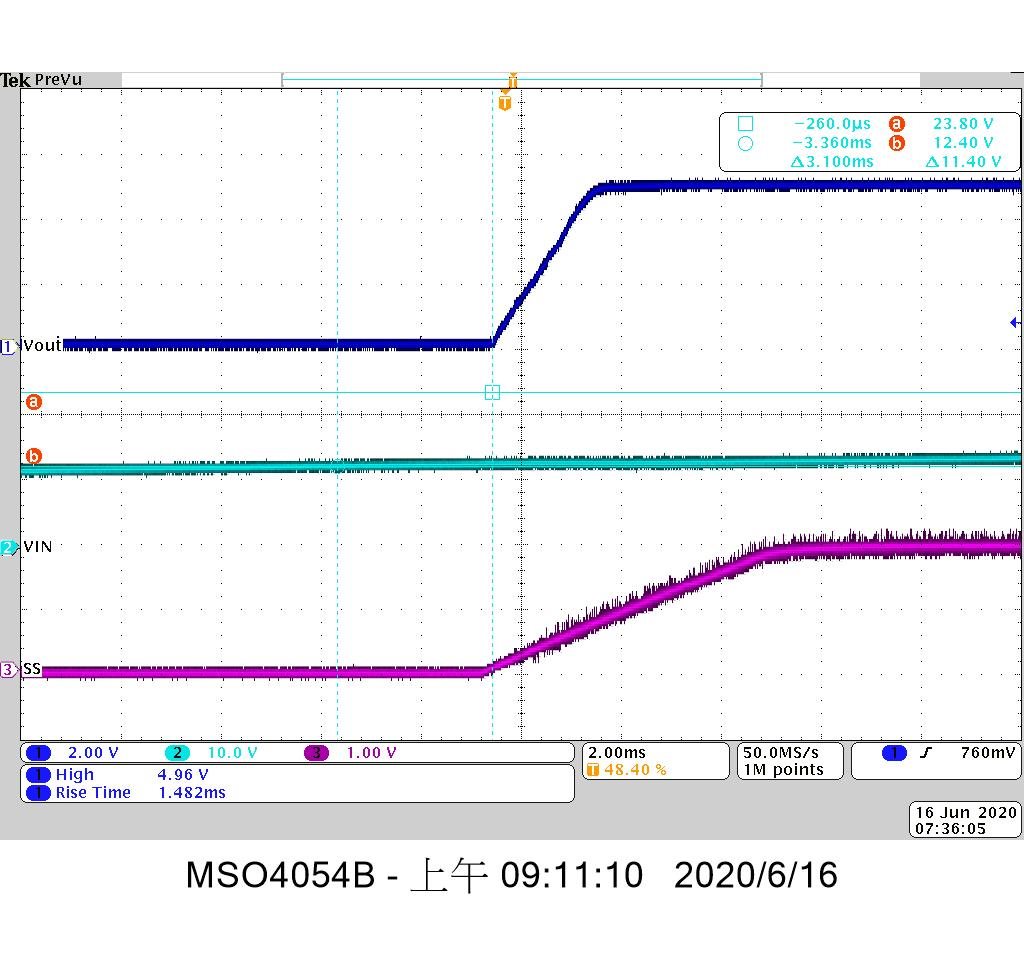

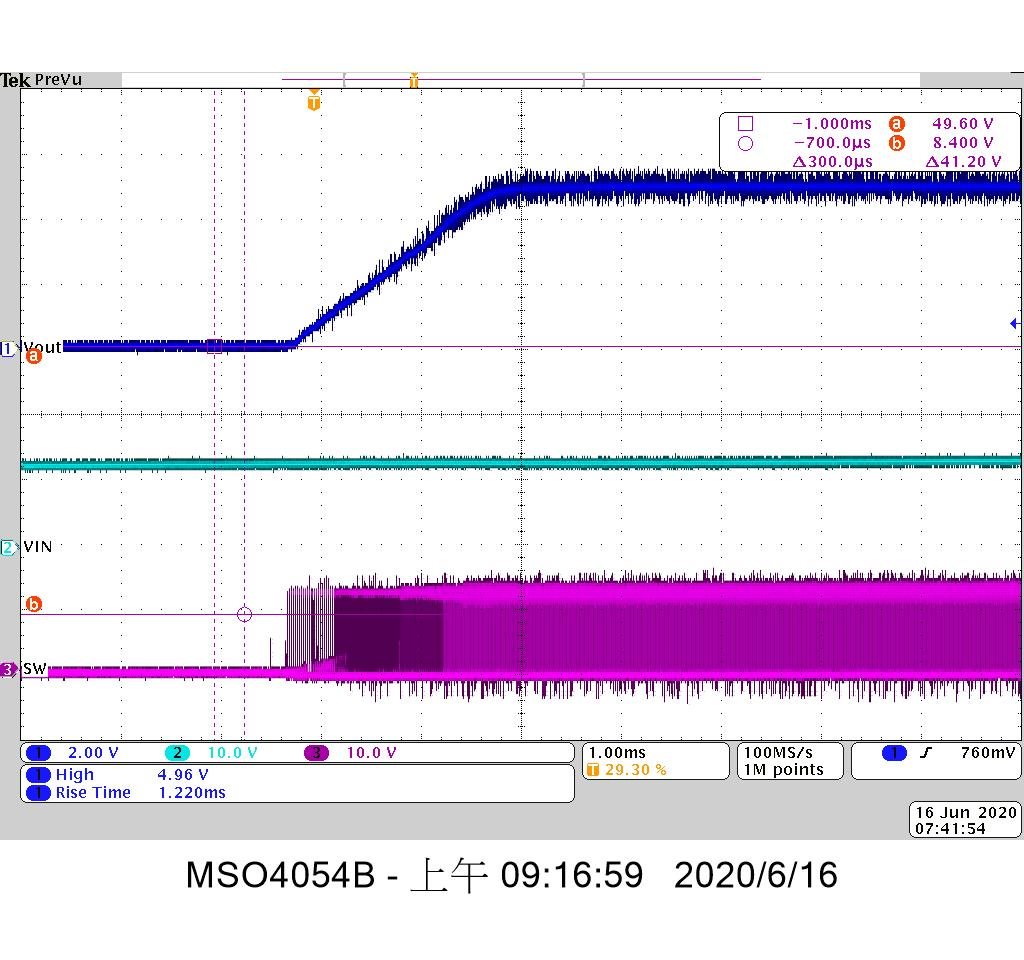

2. CH1 VOUT 5V (LMR14030)