Hello,

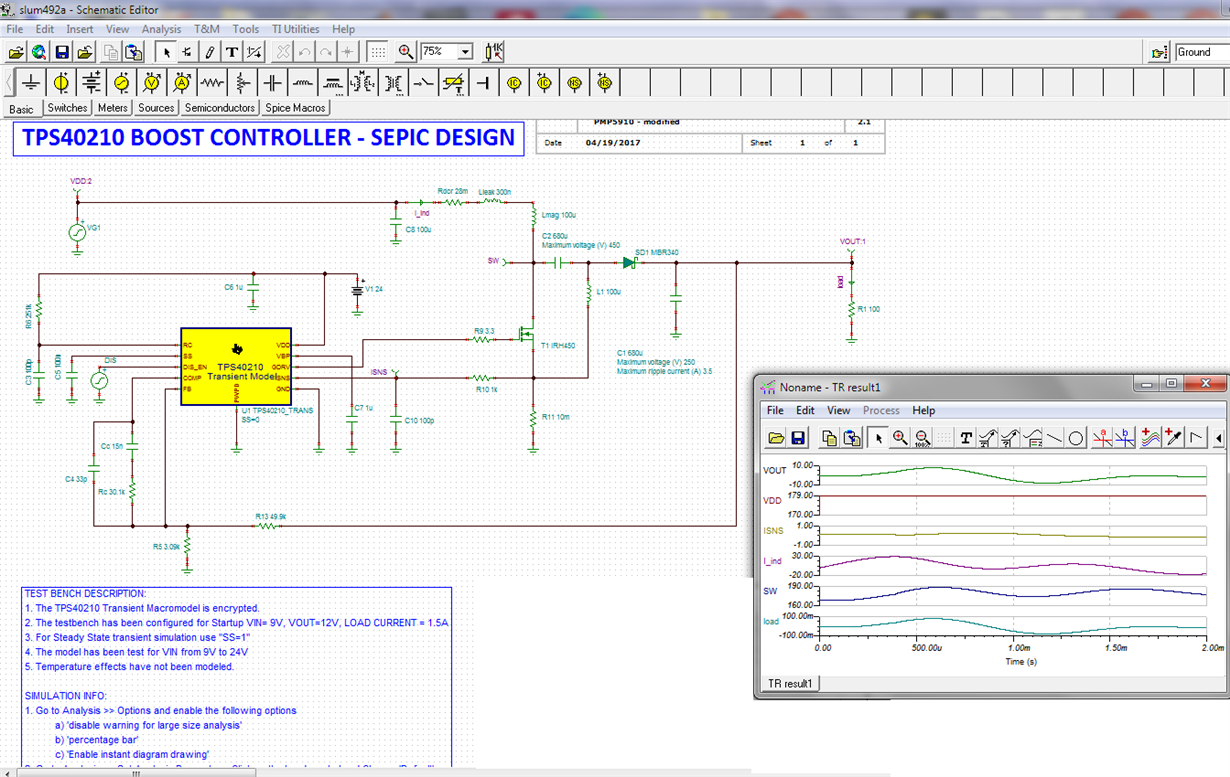

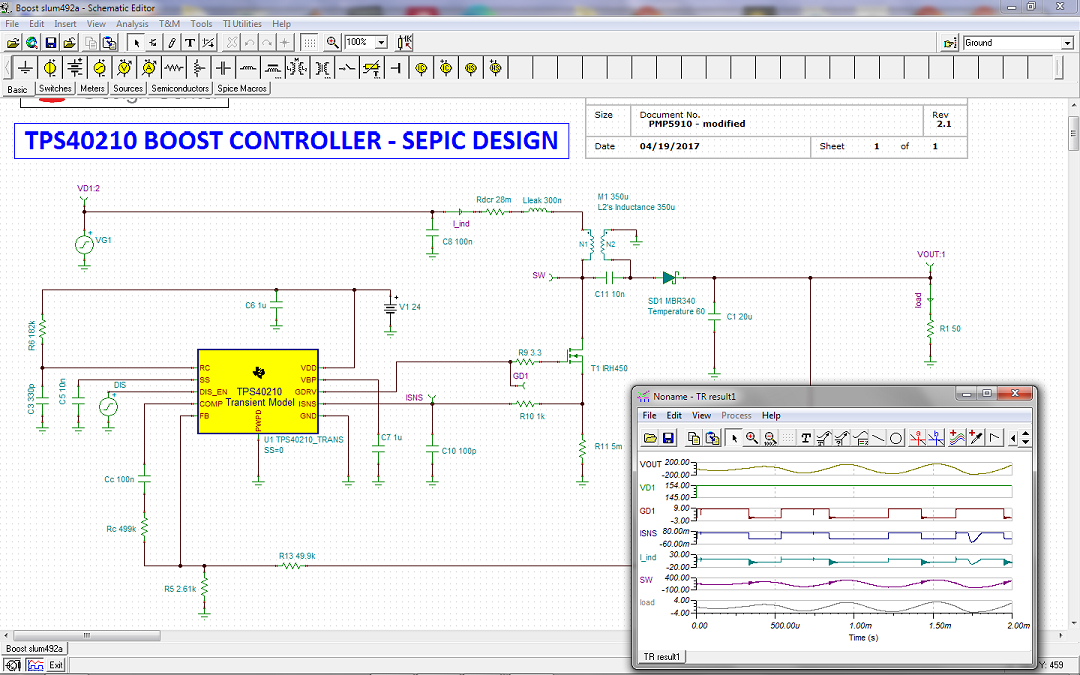

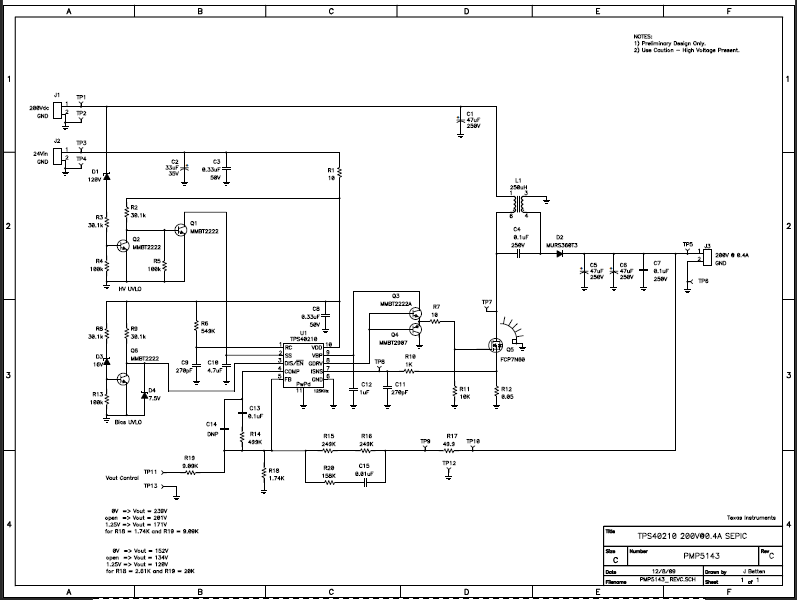

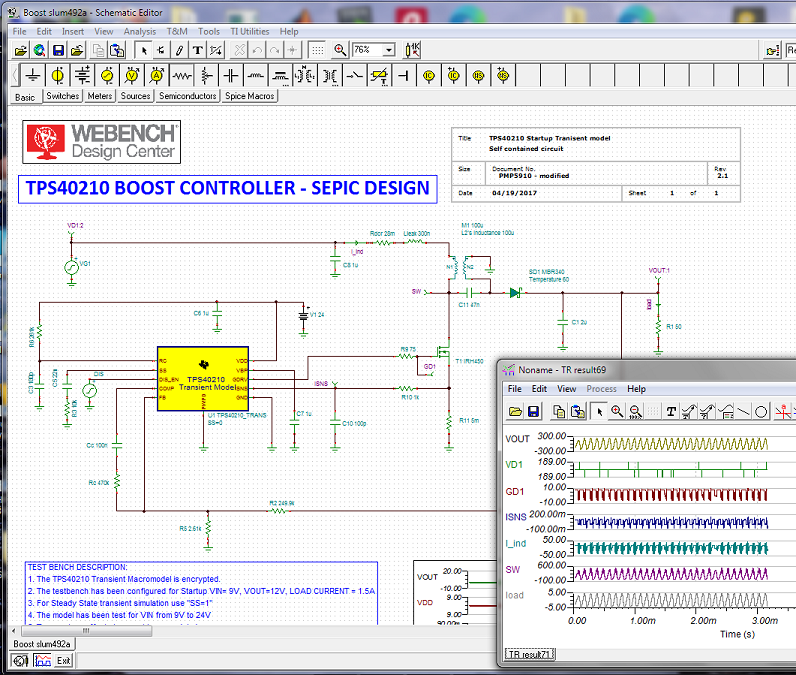

Attempting to develop SEPIC boost regulator Tina simulation via slum942a.tsc or tps40210_Trans.tsm downloads but there is no gate drive signal PWM being plotted. Web Bench also will not begin to build a circuit where +24v VDD is isolated from the NFET drain supply >170v. The NFET sources near ground so there should be no need for external Qg boost driver or switched Totem pole for isolation reasons.

Should it be possible to simulate various boost configurations with GDRV PWM transient analysis output being plotted? Oddly Power Bench SEPIC model predicts the NFET drain voltage reaches 410v and that is also very low. All working voltages on discrete devices (SD1, C2 etc) were raised to or above VG1 and or changed to various capacitance C2 (10n-680u) produced same nonsense plots oscillator RC 150Hz-300Hz

Thanks

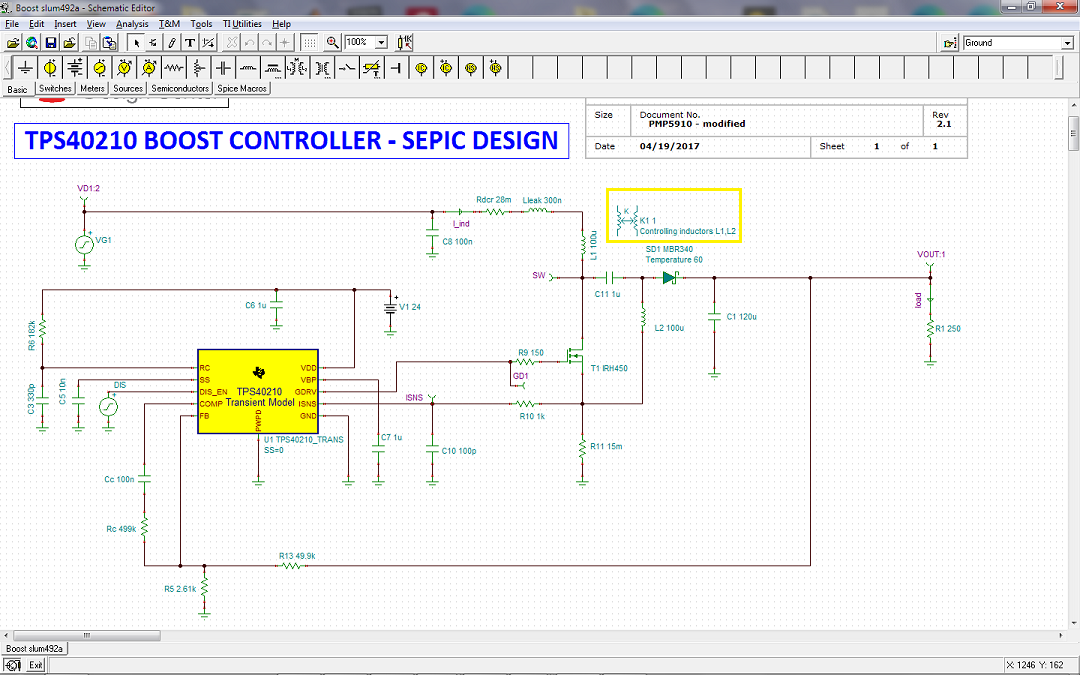

Coupled T1: