Other Parts Discussed in Thread: UCC25640

Hello,

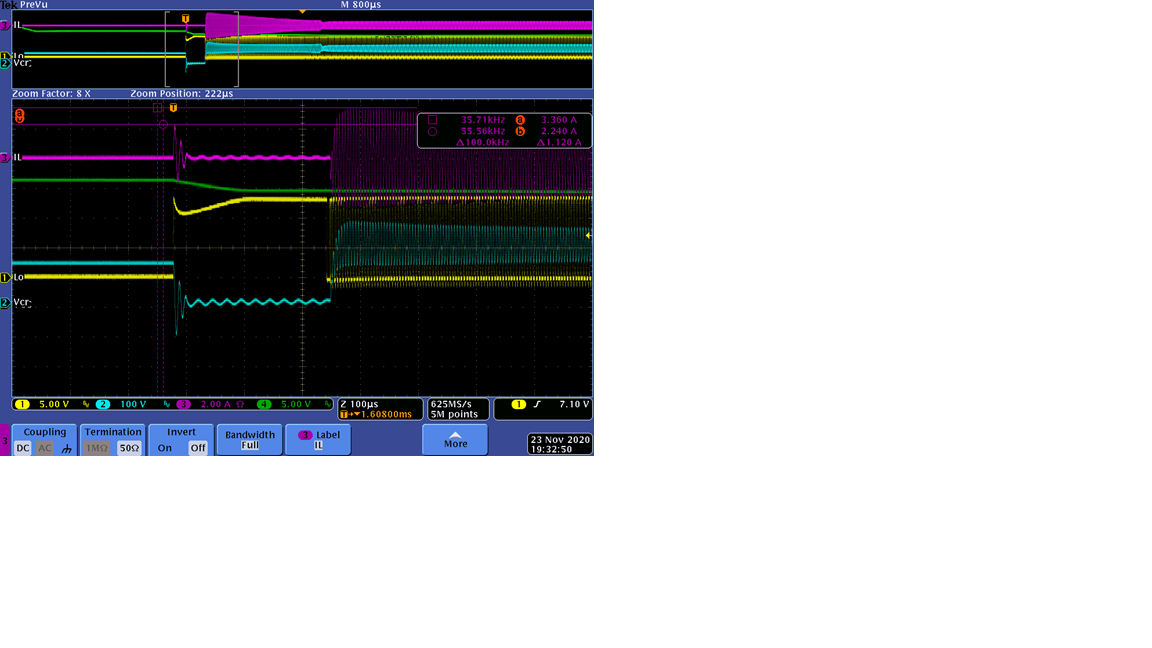

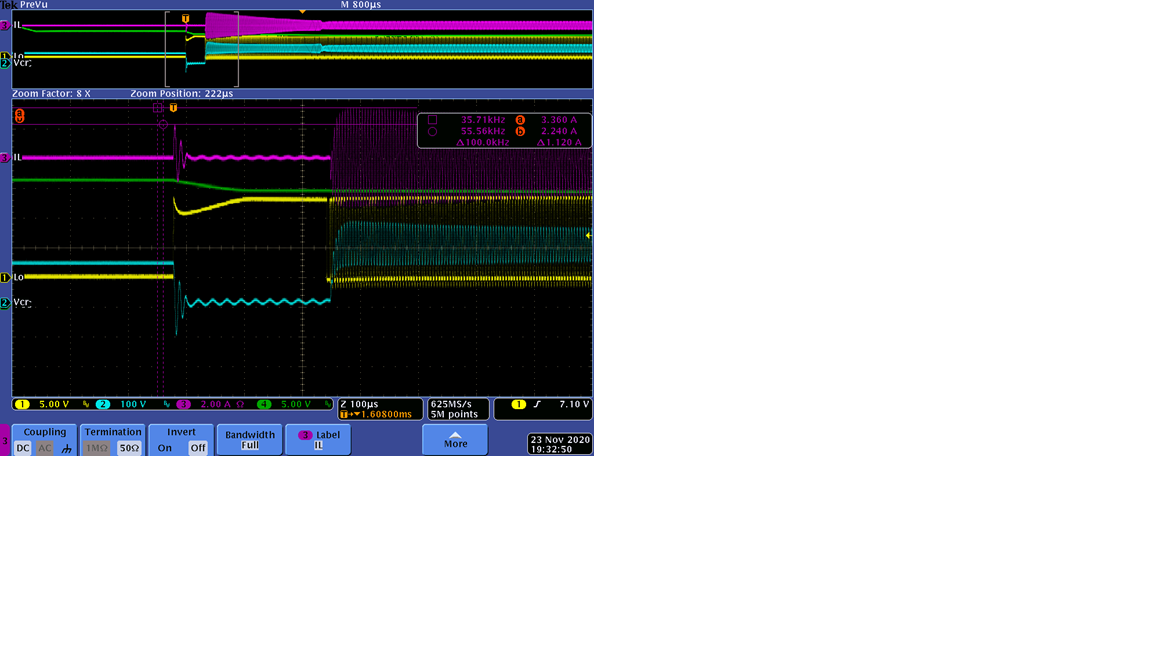

I have a few questions about the pin LL/SS setting and LO gate pulse during charge boot stage.

1. Will the SS initial voltage setting still be valid when ZCS event is triggered?

2. As I read through 03/2020 revision datasheet on BMTH setting by LL/SS pin on page 38, a few descriptions confuse me. I can't find the RLL in block diagram neither on page 38 nor page 18. In the description copied below, is Rfb a typo? should Rfb be RLL?

3. It looks like before converter startup, the LO gate signal will be high for about 265us to charge boot cap, then soft startup initiates. This means split resonant cap topology can't be used with the controller, right?

Thanks.