Other Parts Discussed in Thread: LM3671

Hi,

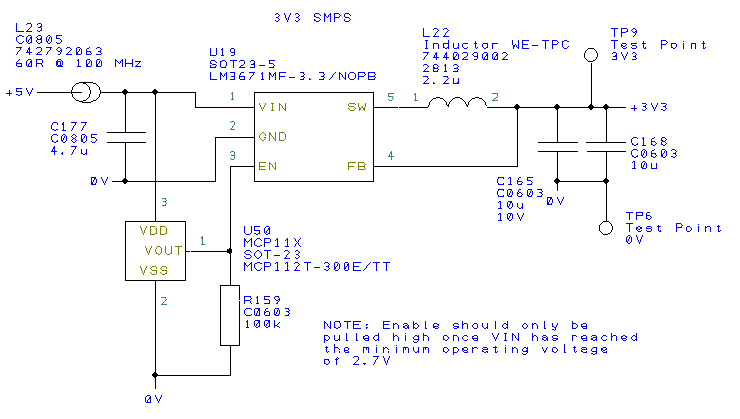

We use the LM3671MF-3.3 in a design that has shipped around 2000 units. I have recently had three boards fail with the output of the LM3671MF-3.3 a low resistance (0.5 to 3 ohms). After swapping just this part the board is functional again.

Prior to swapping I checked for solder joint issues or visible damage elsewhere. To be sure I reflowed the joints and retested but in this case the output seems shorted and the power supply does not start up despite 5V on the input.

In this design I have enable tied to VIN which I found is not recommended (I have another post asking about the risks of this). However I have performed full load step tests, power on/off tests, steady full load tests and current limit tests and the part seems to maintain regulation and function within expected limits.

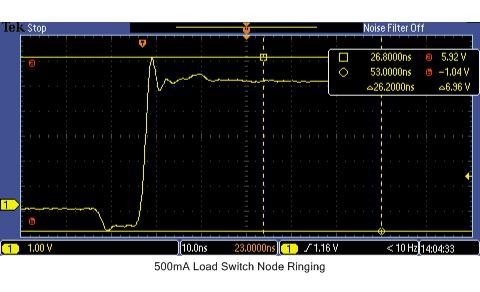

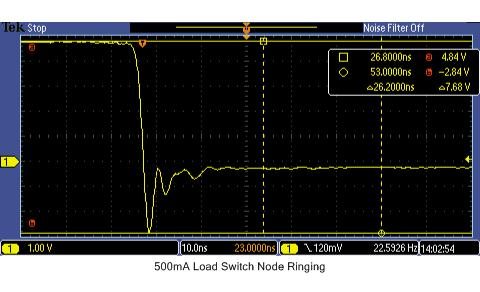

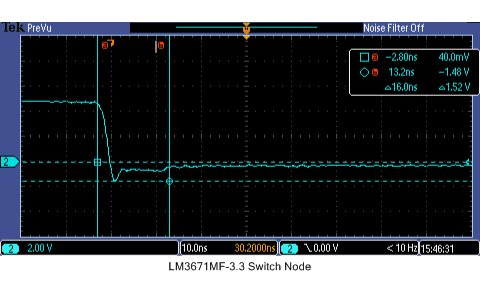

As this is a synchronous design I am wondering if this could be a failure of the rectifier FET.

I wondered if anyone could possibly provide some insight into what could cause the switch node to be near short circuit to 0V.

I had a thought about whether there was a chance the 3.3V switch node could be powered while the input 5V supply was off but I cannot see this in measurement or studying the design. Is it worth adding a diode from output to input (I guess the internal PFET has one) in such designs to make sure power on the output bypasses the device?

Thanks in advance, Mark