Part Number: TPS23861

Tool/software: Linux

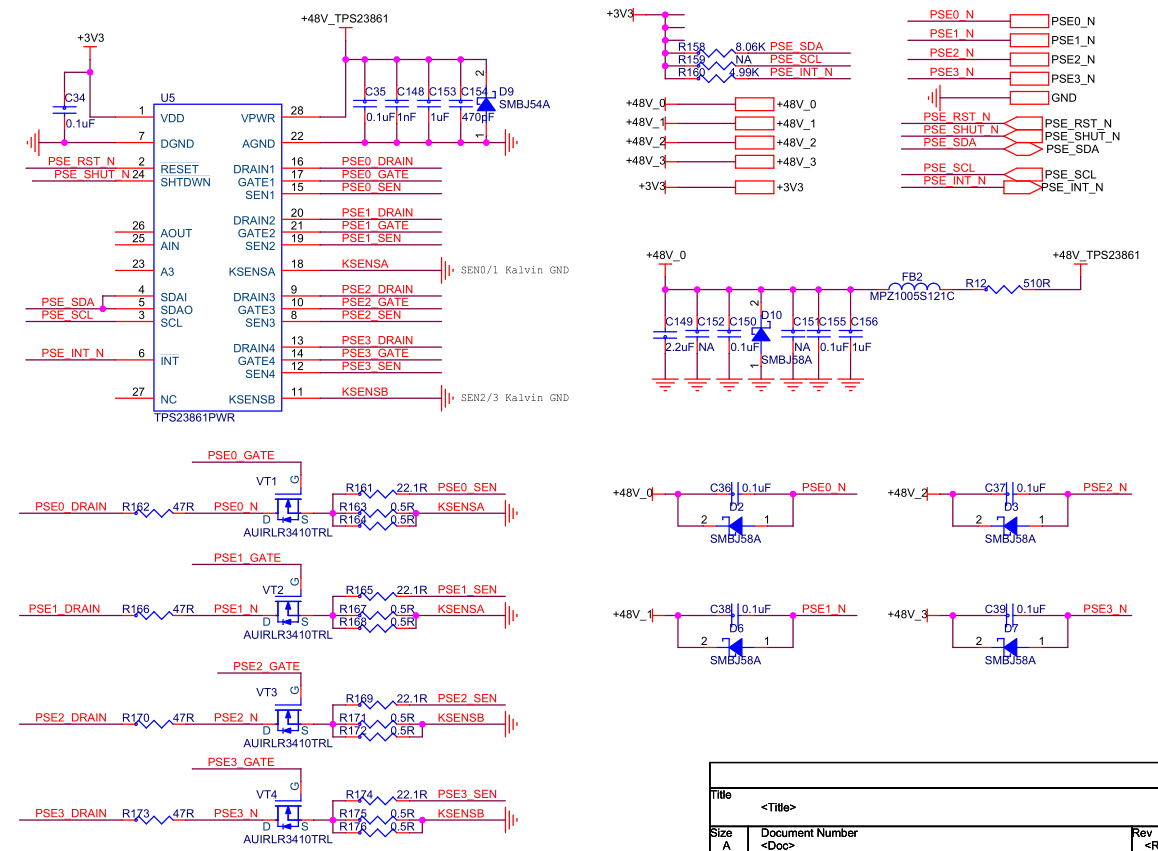

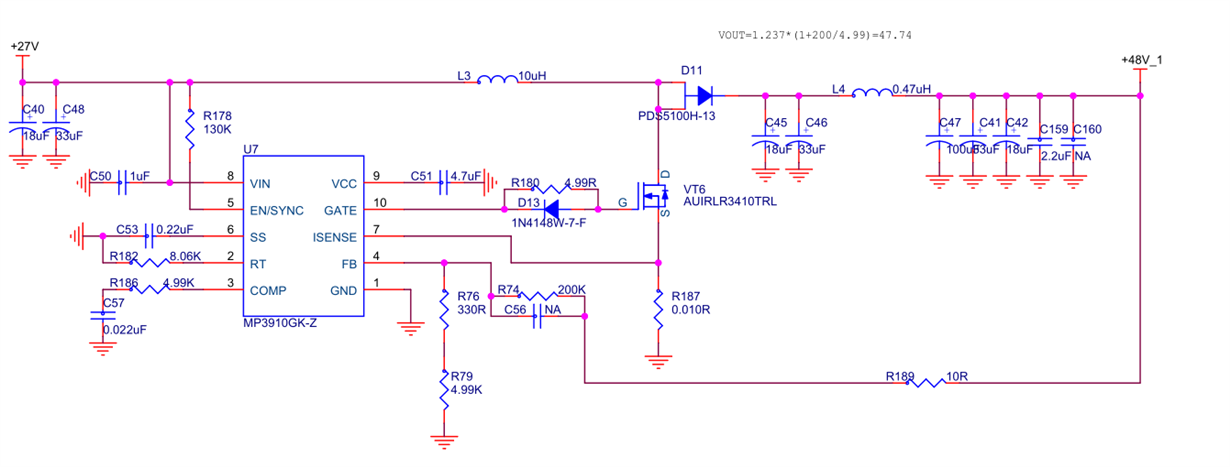

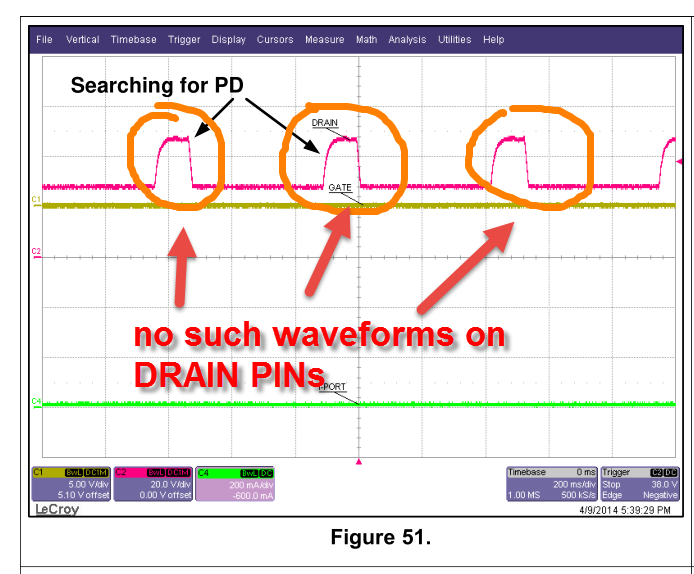

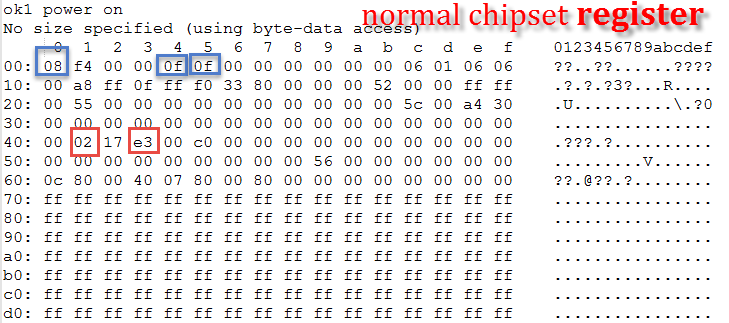

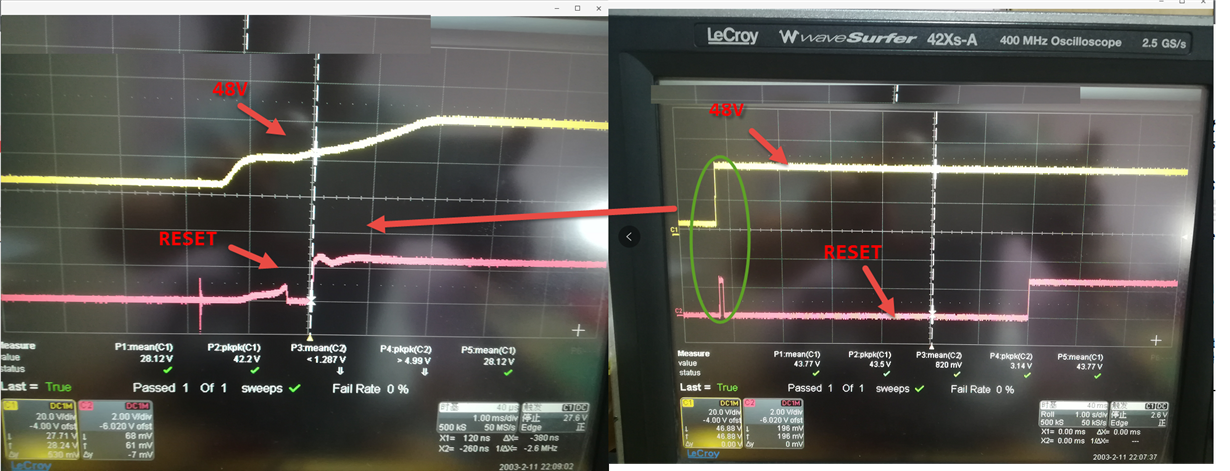

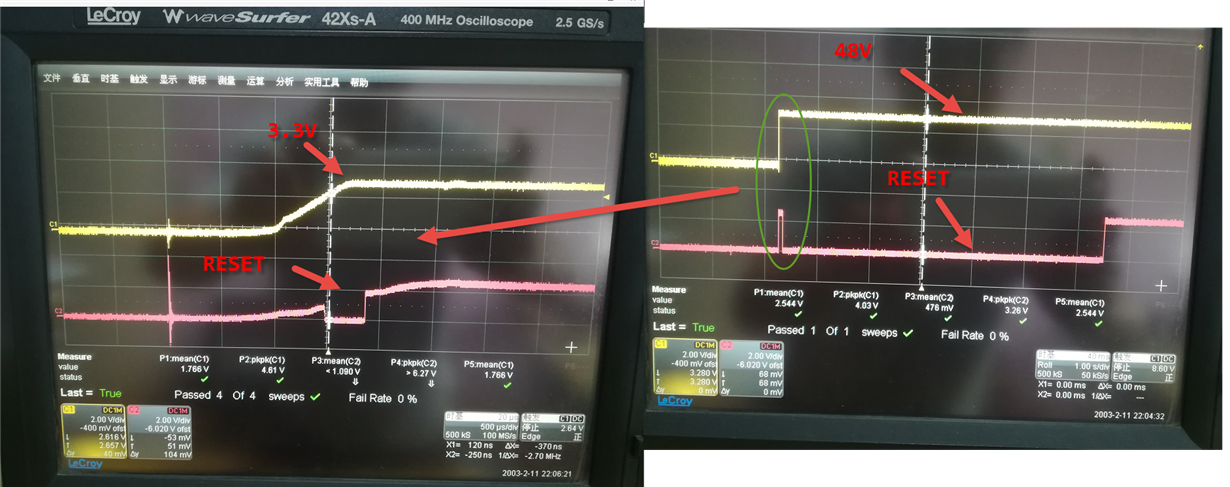

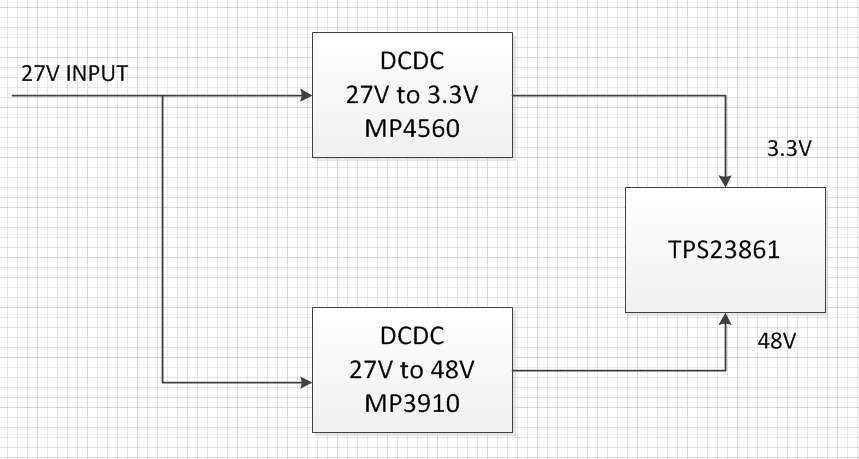

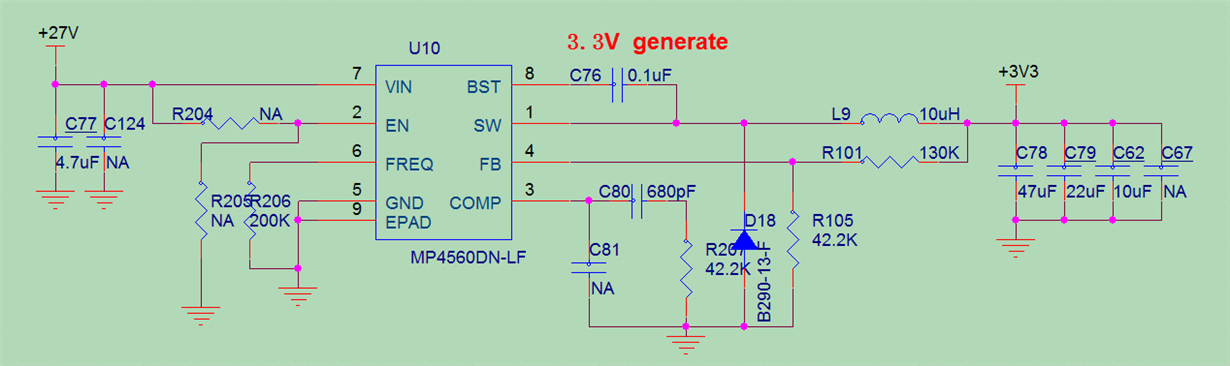

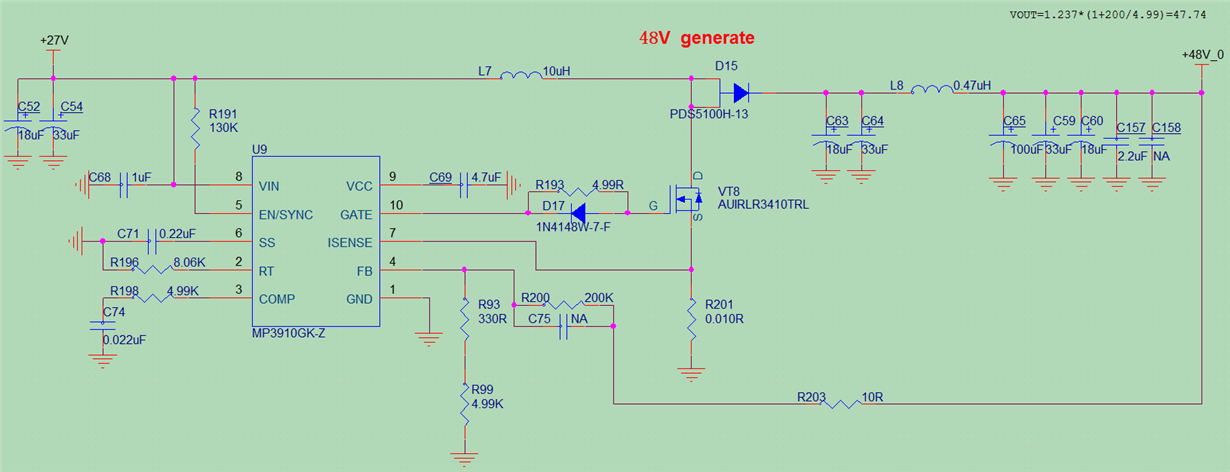

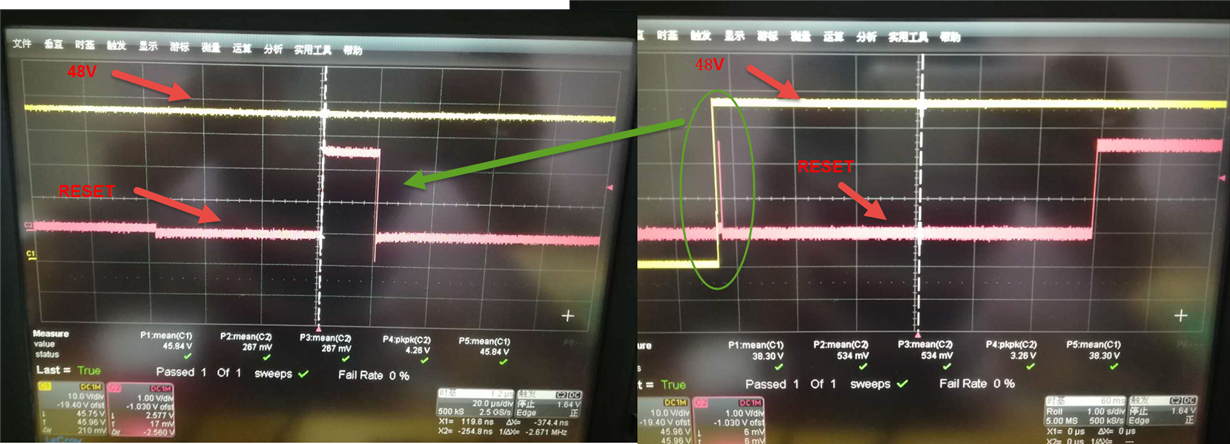

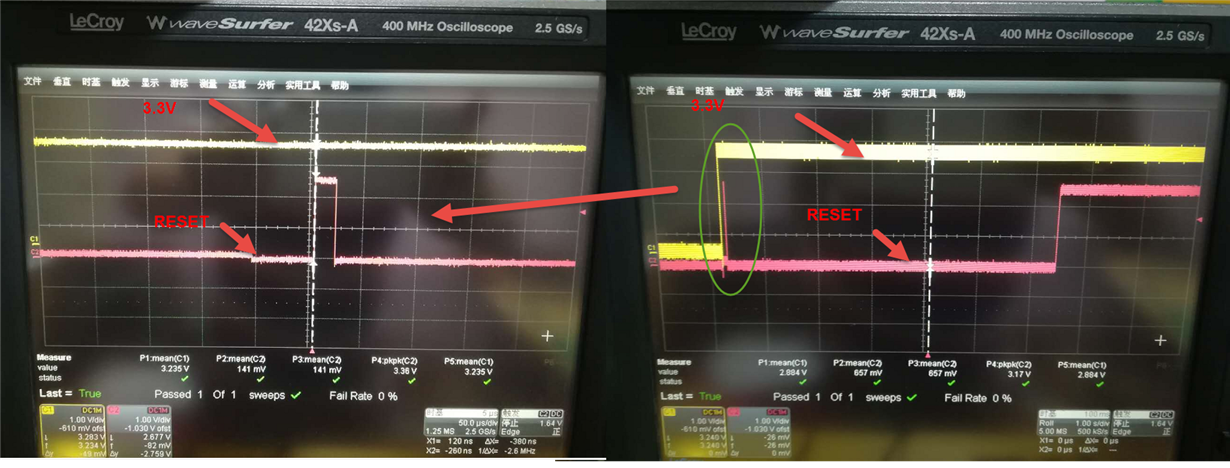

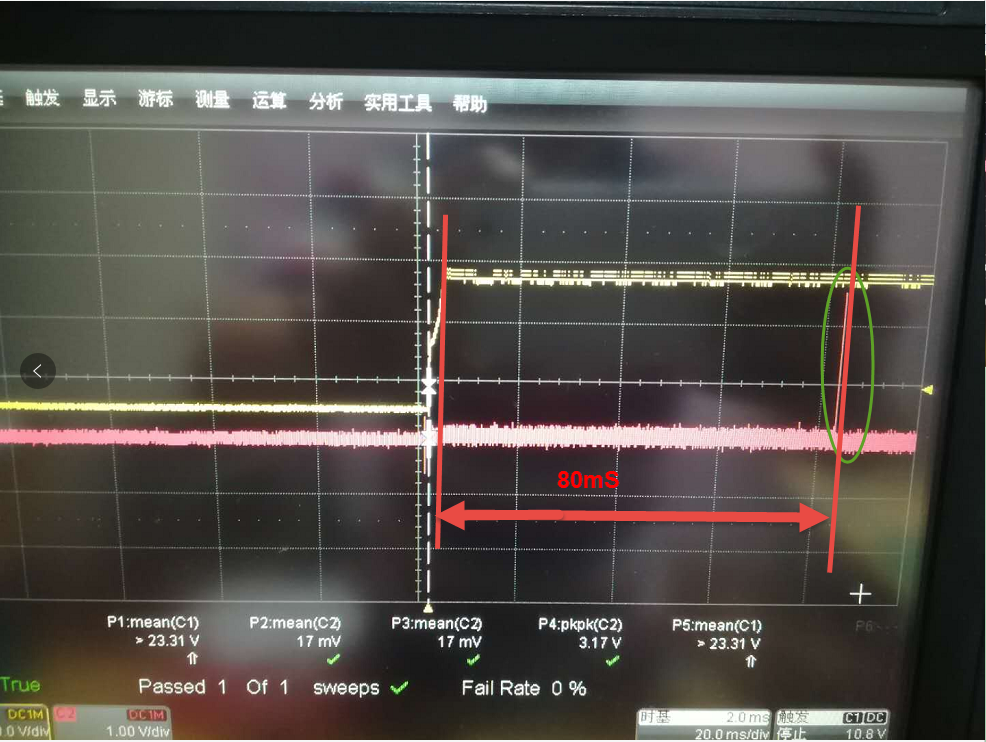

We have a problem with TPS23861 chipset. We have been using this chipset in our project under normal environmental temperature. After 24 hours of continuous running, about 2.5% of our entire batch of 1000 pcs would exhibit failure. The PoE would not be able to detect our PD device and supply electricity to our board.