Tool/software:

Hi TI Experts

I see the below status on TI.com for AM62L

Can you provide additional inputs on the collaterals to be referred or guidelines to follow during custom board design

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi TI Experts

I see the below status on TI.com for AM62L

Can you provide additional inputs on the collaterals to be referred or guidelines to follow during custom board design

Hi Board Designers,

Refer below:

FAQs

Core

Peripherals

EVM

Design

Other E2Es for reference:

Bootmode

(+) AM62L: AM62L emmc - Processors forum - Processors - TI E2E support forums

Can you please confirm if the XAM62L32BOGHAANB silicon revision (or the corresponding software/ROM version) officially supports the Reduced Pincount (RPC) boot mode for eMMC as depicted in our configuration?

Please refer to the e2e on booting from eMMC boot partition with reduced boot mode on AM62L SR1.1 SoC.

RE: AM62L: eMMC boot failure in reduced pin mode

he issue has been resolved after testing confirmed it was caused by missing the step which to set boot from boot0.

This is a known issue, errata is in the process of being updated. Your observations align with ours, in that several different types of SanDisk cards fail, while cards from other manufacturers boot successfully. For silicon revision 1.0, there is not a robust workaround, other than to continue using the working cards. We have also seen that if you set both primary and backup to SD card boot, sometimes the backup boot will be successful on certain card that failed the primary boot

As per the Errata i2473 Boot: eMMC boot may fail, outlined in the “AM62Lx Sitara Processors Silicon Errata, Silicon Revision 1.0” document, the recommended workaround is to utilize eMMC boot via UDA.

In our SOM design, we support only the reduced pin count boot mode, where eMMC boot is limited to the MMC0 (eMMC) Boot Partition. While we have provisions for booting from a microSD card—which we are currently utilizing—eMMC boot support is mandatory for us. Currently, we do not have an option to enable eMMC boot using UDA.

We would like to confirm whether this erratum will be addressed in the next silicon revision and if Yes, the issue is fully root caused, and the fix is being implemented for next silicon revision.

Yes, the eMMC boot from boot partition (once the issue is fixed) is supported via reduced boot pin configurations.

DDR4

eMMC

SD card

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1502807/am62l-spi-voltages

The FAQ is being updated.

Please review the FAQ frequently for updates.

Regards,

Sreenivasa

Hi Board Designers,

Refer below additional information:

DDR4 memory addressable range

The device was targeted for lower cost industrial applications; thus package was optimized, and some DDR pins were sacrificed, including one of the CS pins. This only allows single rank designs (AM62x has 2CS for dual rank designs), which halved the maximum address reach for DDR.

Note LPDDR4 max is 2GByte, but DDR4 max is 4GByte

The DDRSS does not support DDR0_ALERT_n, DDR0_PAR, DDR0_CKE1, DDR0_CS1_n, DDR0_ODT1 signals (pins). It is recommended to follow the memory data sheet recommendations to connect any of the available signals that are not interfaced to the processor DDRSS

AM62L - SOC Package Delays for DDR interface

Refer AM62x, AM62Lx DDR Board Design and Layout Guidelines.

AM62L31, can the integrated switch be run in totally unmanaged mode if e.g. the 62L31 CPU boot fails and is not able to do any configuration to the switch?

Minimum requirement would be the capability to forward the traffic between the external RGMII ports.

No. At boot the Ethernet ports are configured as just ports, not as a switch. Further the subsystem is not reset-isolated in hardware, so there is no guarantee that in all cases the switch keeps operating regardless of what happens on the A53's. So there will be an interruption of the switching function for the duration of the SoC reset and operating system boot.

GPMC interface modes supported

Supported GPMC configuration includes 16-bit (GPMC, Raw NAND, Muxed-NOR). The GPMC signal names are representative of the IP functionality rather than the supported functionality. Non-multiplexed Address and Data interface mode is not supported.

Does the AM62L support the redundant copies of the first stage boot loader at UDA for eMMC?

Please refer to the section “5.4.3.1 eMMC Bootloader Operation” of the TRM. It mentions that the ROM supports booting the redundant image at offset 0x400000 incase the booting fails from the primary offset 0x0 for the UDA RAW mode only.

For the UDA FS mode, the ROM doesn’t have the redundant boot support.

If you are booting Linux then you may not use the UDA RAW mode as the primary offset 0x0 conflicts with the partition table required for the filesystems.

So, the feasible option is to use UDA FS mode for which the ROM doesn’t have redundant boot support.

Regards,

Sreenivasa

I also see a corresponding User Guide: Hardware Design Considerations for Custom Board Using AM62L32 and AM62L01 Processors available under AM62L-PROCESSOR-SDK Software development kit (SDK) | TI.com. Adding in case this isn't covered by the above content and if it serves as a good reference for the related matter.

Thanks,

Harshit

Hello Harshit,

Thank you for the inputs and this help. Appreciate your input for improving the collateral.

FYI, we have the above referenced file and other key collateral links included in the below FAQ

Regards,

Sreenivasa

Hi Board Designers,

Refer below inputs regarding eMMC support for SR1.1

AM62L: eMMC boot failure in reduced pin mode

As noted from <Table 5-3. BOOTMODE Pin Mapping (Reduced)> in AM62L TRM https://www.ti.com/lit/pdf/sprujb4

BOOTMODE[15:12] = 1011 => Fixed 4 => eMMC Boot Partition (primary) MMC (backup)

BOOTMODE[15:12] = 1010 => Fixed 3 => MMC/UDA (primary) UART (backup)

BOOTMODE[15:12] = 1000 => Fixed 1 => eMMC Boot Partition (primary) USB-DFU (backup)

As noted from <Table 1-2. Advisories Matrix> in AM62L Errata https://www.ti.com/lit/pdf/sprz582, there're eMMC boot issues from eMMC boot partition in AM62L PG1.0 ROM, and your test struck the eMMC boot issues.

With AM62L PG1.1 fixes on ROM as noted in <Table 1-2. Advisories Matrix> in AM62L Errata https://www.ti.com/lit/pdf/sprz582, I'd recommend re-run your test on AM62L PG1.1 silicon.

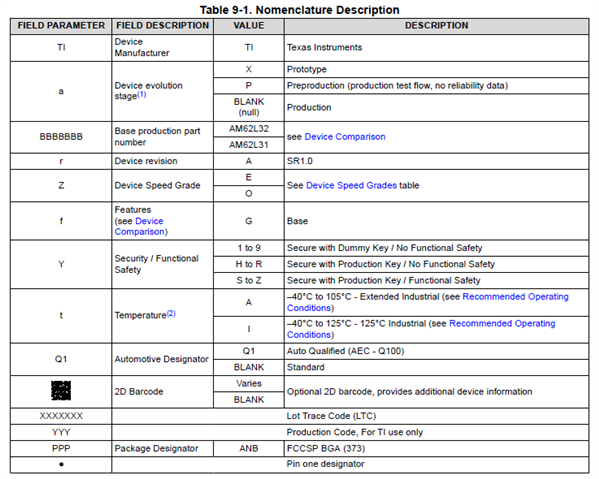

In reference to <Table 9-1. Nomenclature Description> in AM62L datasheet https://www.ti.com/lit/ds/symlink/am62l.pdf, The <Device revision> field increments from "A" to "B" for SR 1.1 silicon.

Please work with TI local team on how to order AM62L SR 1.1 silicon.

Regards,

Sreenivasa

(+) AM62L: MMC - Processors forum - Processors - TI E2E support forums

HI Board Designers,

Inputs related to supported standards

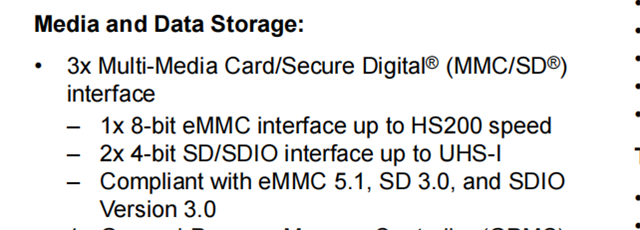

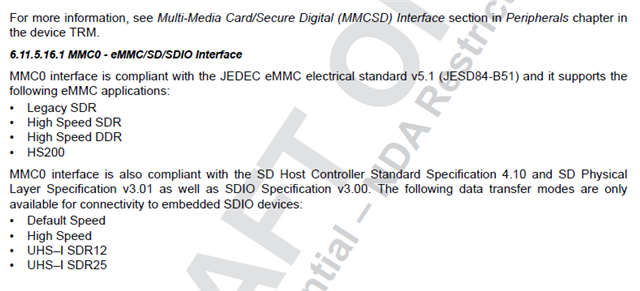

Do all three MMC/SD buses support eMMC 5.1, SD 3.0, and SDIO Version 3.0?

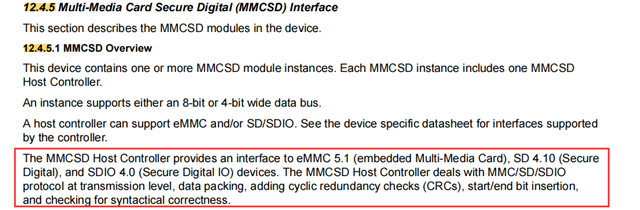

2、What does the content shown in the following picture mentioned in the TRM manual mean? Does it support SD 4.10 and SDIO 4.0? So, should we follow the data manual or the TRM?

The next revision of the AM62Lx datasheet will be updated to show with the following list of devices and data transfer modes supported for each MMC instance.

The MMC0 port supports connections to an eMMC device or embedded SDIO device. It does not support removable SD Cards.

The MMC1 and MMC2 ports support connection to a removable SD Cards or embedded SDIO device. They do not support eMMC devices.

What does the content shown in the following picture mentioned in the TRM manual mean? Does it support SD 4.10 and SDIO 4.0? So, should we follow the data manual or the TRM?

For the SDIO specifications, please follow the data sheet.

The references to 4.x in the TRM will be updated.

egarding the MMC interface of AM62Lx, does MMC0 support a 1-bit wide data bus or a 4-bit wide data bus? And do MMC1 and MMC2 support a 1-bit wide data bus?

Is this a generic query or do you have an use case for the query.

As a general answer, MMC0 should be able to support 4-bit or 1-bit and MMC1/MMC2 should be able to support 1-bit.

I ever have similar support needs to support 2 eMMC, even one can be 4bit mode. which was supported on AM335x, but new AM62x can only support one, is it just not verified/tested? or the IP can't support 4-bit eMMC on MMC1?

eMMC is only supported on MMC0. We did not close timing of any other MMC port to be compliant to the eMMC timing requirements.

Regards,

Sreenivasa