Dear Experts,

The custom board design housed with an AM3359 processor connected with an FPGA over GPMC interface, which is operating at 100MHz, Synchronous & Multiplexed mode, in AD (Address & Data: 16 bit) configurations.

The AM3359 processor is running with Linux SDK v6.1.

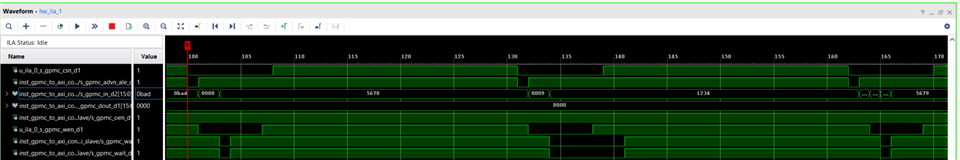

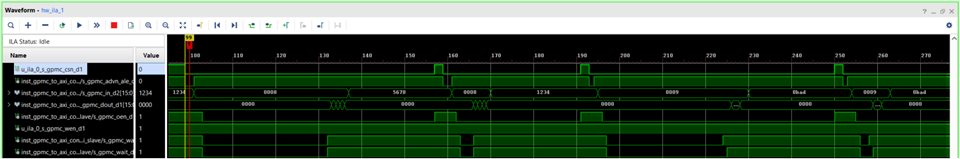

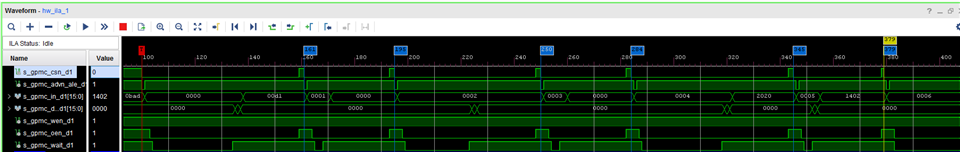

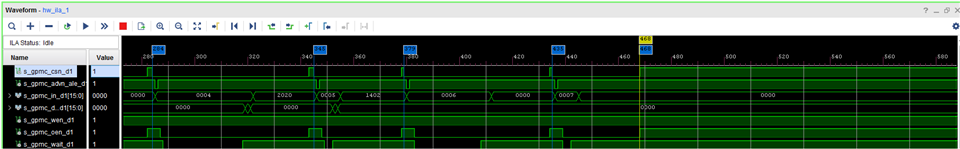

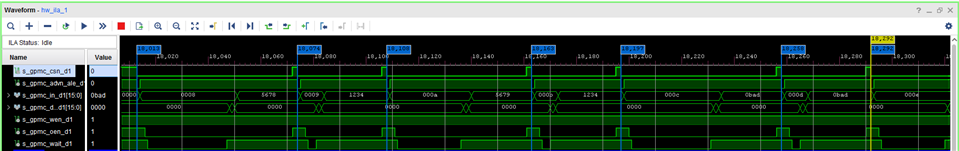

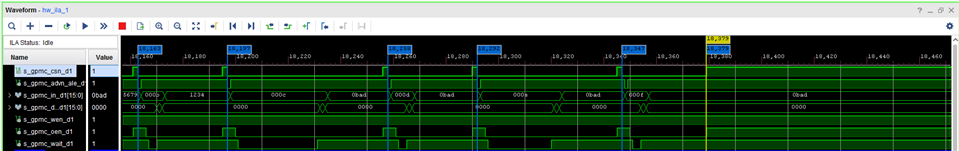

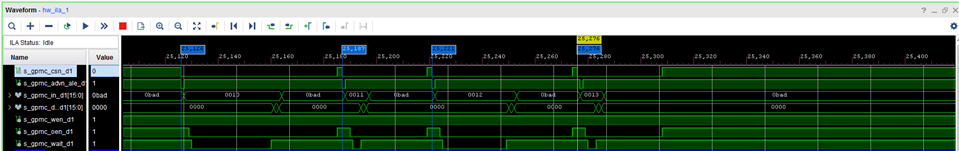

There is an issue with read transactions with address field increment is improper. Whereas, for write transactions the data & address field are proper.

- Read transaction: Address (ex. 0x10000008) + LSB Data + Address (ex. 0x10000008 - Expected address is 0x1000000A) + MSB Data + Address (ex. 0x1000000A - Expected address is 0x1000000C) + LSB Data + Address (ex. 0x1000000A - Expected address is 0x1000000E) + MSB

Write transaction: Address (ex. 0x10000008) + LSB Data + Address (ex. 0x1000000A) + MSB Data + Address (ex. 0x1000000C) + LSB Data + Address (ex. 0x1000000E) + MSB

The GPMC interface configurations followed are,

0x50000010 0x00000008

0x5000001C 0x00000200

0x50000040 0x00001FF0

0x50000050 0x00000010

0x50000054 0x00000000

0x500000F0 0x2A651200

0x500000F4 0x00081D00

0x500000F8 0x00010100

0x500000FC 0x08021D03

0x50000100 0x01081F1F

0x50000104 0x820302C0

0x50000108 0x00000001

0x50000108 0x00000f50

Attached the screenshots of the Write and Read transactions.

Please help to correct the configurations and make read transactions proper.