Hi TI

Customer considered SK Hynix LPDDR4 H54G46BYYV 16Gb device to replace Micron MT53' 32Gb device which has been applied to TI Jacinto EVM.

I attached datasheets for both devices.

I could not distinguish btw Micron and SK Hynix regarding bit width. I am not sure why Micron device is 32 bit and SK Hynix device is 16 bit even both use the same 16 DQ I/O width.

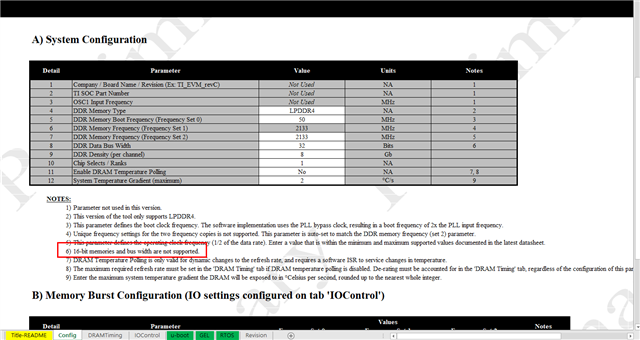

I am asking I found the following restriction statement from DDR config Tool as below.

"16-bit memory and bus width not supported"

Please let me know why Micron' MT53 is 32bit memory and Hynix' H54G46 is 16 bit.

Thanks.

200b_z11m_ddp_qdp_auto_lpddr4_lpddr4x.pdf

1781.Automotive_DA 16Gb LPDDR4_H54G46BYYV(Q,P)X053_Rev1.1.pdf