Other Parts Discussed in Thread: TMS320C6655, , PROCESSOR-SDK-C665X

Hi TI

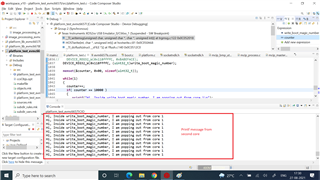

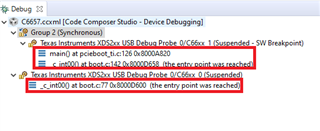

Can I find the encoding or any documentation on the format of the BOOT MAGIC register.

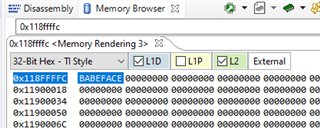

The only information i can find is on the test code of the evaluation board that this register has the address: 0x8ffffc

I have searched over all documentation but i can't find any description of such an important register of the the bootloader process

Can you please help.

BR

Tam Tran

Vestas Wind System