Dear

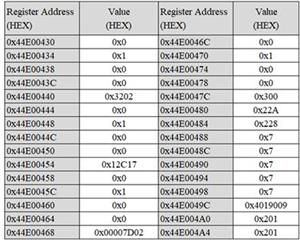

Hardware platform(AM3352ZCZA80+MT41K256M16TW-107).

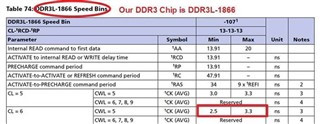

Currently , we have another urgent topic about the DDR test item—Tck(avg)

This spec limitation is from 2.5ns~3.3ns, As you know,AM3352ZCZA80 support DDR3-800

So our clk is 400Mhz and the period is about 2.5ns, this test item is always fail.

My question is: Can we set the clk as less than 400Mhz(39?Mhz?)