Part Number: TDA4VM

Hi

TI Soupport team,

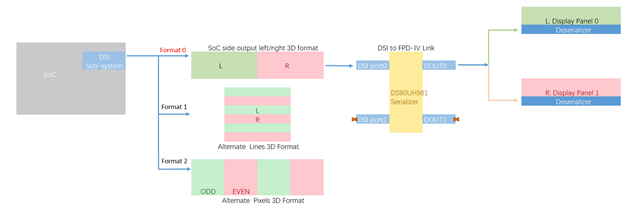

From above picture, Our custom board want to realize the ultimate goal. Got some questions need to comfirm.

I、From SoC side, Is it possible the DSI sub-system output these three modes OR one of the three Farmat ?

1、We used PDK_80, The default output format by DSS is Left/Right format ? How to modify it to other format (in vision-app or dss driver pdk/packages/ti/src/dss/) ?

II、We used DS90UH981 serializer, Received (1280 * 2) *480 image from SoC DSI sub-system, My ultimate goal is that to use split mode inside UH981 for two display panel respectively.

Each display panel receive 1280 * 480.

1、Refer to the content of this link( https://e2e.ti.com/support/processors-group/processors/f/processors-forum/942679/faq-processor-sdk-dra8x-tda4x-how-to-change-display-resolution-in-vision-apps )

to modify DSI output resolution (1280 * 2) * 480 to UH981. Is the modification correct ?

vision_apps\apps\basic_demos\app_multi_cam\app_display_module.c

displayObj->disp_params.outWidth = 1280 * 2;//DISPLAY_WIDTH;

displayObj->disp_params.outHeight = 480;//DISPLAY_HEIGHT;

displayObj->disp_params.posX = (1920-DISPLAY_WIDTH)/2;

displayObj->disp_params.posY = (1080-DISPLAY_HEIGHT)/2;

vision_apps\apps\basic_demos\app_tirtos\common\app_init.c

prm.timings.width = 1280 * 2U;

prm.timings.height = 480U;

prm.timings.hFrontPorch = 16U;

prm.timings.hBackPorch = 48U;

prm.timings.hSyncLen = 40U;

prm.timings.vFrontPorch = 5U;

prm.timings.vBackPorch = 3U;

prm.timings.vSyncLen = 5U;

prm.timings.pixelClock = 39400000ULL;

2、For now, because we don not kown the Deserializer, Any possible to let me kown how to config UH981 for split mode ?

And is there any scripts to achieve my ultimate goal ( Split (1208 * 2)*480 to two 1280 * 480 ) , how to modify program(in vision-app or dss-driver) ?

It would be best that you can offer a script to set up UH981 for single display panel (non-split mode). Just to verify the whether the data pathway properly under PCB !!

Best Regards

Murphy,