Hi TI,

I need some help on understanding MPU Config and the different options TI provides. I am using PSDK RTOS v08.00. In specific, I want to understand, which options to choose when configuring some memory region as either

- Strongly Ordered Memory

- Device Memory

- Normal Memory

To do so, I am using CSL_ArmR5MpuRegionCfg struct to override the default definitions. Here is some default region for reference:

{

/* Region 0 configuration: complete 32 bit address space = 4Gbits */

.regionId = 0U,

.enable = 1U,

.baseAddr = 0x0U,

.size = CSL_ARM_R5_MPU_REGION_SIZE_4GB,

.subRegionEnable = CSL_ARM_R5_MPU_SUB_REGION_ENABLE_ALL,

.exeNeverControl = 1U,

.accessPermission = CSL_ARM_R5_ACC_PERM_PRIV_RD_WR,

.shareable = 1U,

.cacheable = (uint32_t)FALSE,

.cachePolicy = 0U,

.memAttr = 0U,

},

The fields which are confusing to me since they kind of interfere with each other are:

- shareable

- cacheable

- cachePolicy

- memAttr

So lets take a look at the code sample. Here, region 0 has the following options;

- shareable = 1

- cacheable = 0

- cachePolicy = 0 (According to csl_arm_r5_mpu.h, this field is only valid if cacheable is true, so the value written here has no effect)

- memAttr = 0 (CSL_ARM_R5_MEM_ATTR_STRONGLY_ORDERED)

In my understanding, this would declare this specific memory region as "Strongly Ordered", right? Leaving cacheable = 0 untouched, I still have various opions on memAttr, which kind of indicate, that the Cache is going to be activated again, although I explicitly deacitvated it. The options I am speaking of are:

/** \brief Memory type and cache policies: Strongly-ordered. */

#define CSL_ARM_R5_MEM_ATTR_STRONGLY_ORDERED ((uint32_t) 0x0U)

/** \brief Memory type and cache policies: Shareable. */

#define CSL_ARM_R5_MEM_ATTR_SHAREABLE ((uint32_t) 0x1U)

/** \brief Memory type and cache policies:

Outer and Inner write-through, no write-allocate. */

#define CSL_ARM_R5_MEM_ATTR_CACHED_WT_NO_WA ((uint32_t) 0x2U)

/** \brief Memory type and cache policies:

Outer and Inner write-back, no write-allocate. */

#define CSL_ARM_R5_MEM_ATTR_CACHED_WB_NO_WA ((uint32_t) 0x3U)

/** \brief Memory type and cache policies: Non cacheable. */

#define CSL_ARM_R5_MEM_ATTR_STRONGLY_NON_CACHED ((uint32_t) 0x4U)

/** \brief Memory type and cache policies:

Outer and Inner write-back, write-allocate. */

#define CSL_ARM_R5_MEM_ATTR_CACHED_WB_WA ((uint32_t) 0x5U)

/** \brief Memory type and cache policies: Non-shareable Device. */

#define CSL_ARM_R5_MEM_ATTR_NON_SHAREABLE ((uint32_t) 0x6U)

/** \brief This should be passed to configuration. */

#define CSL_ARM_R5_MEM_ATTR_MAX ((uint32_t) 0x7U)

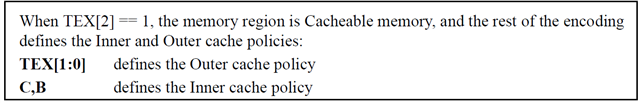

Q1: Can you please elaborate on the different memAttr options? For instance, what exactly is configured, when setting memAttr = CSL_ARM_R5_MEM_ATTR_CACHED_WB_WA while at the same time cacheable is set to 0? Is Cache activated again? This would lead to questioning the purpose of "cacheable" option.

Q2: Is it necessary to set shareable to 1 when I want to declare some memory as Strongly Ordered/Device/Normal? What effect does shareable in general have on the memory?

Q3: What should be configured and how, if I want to declare a memory region as Device or Normal memory? Do I have to use CSL_ARM_R5_MEM_ATTR_SHAREABLE?

Thanks for your help and best regards,

Felix