Hi Support Team,

Here are questions from my customer about the intermediate potential.

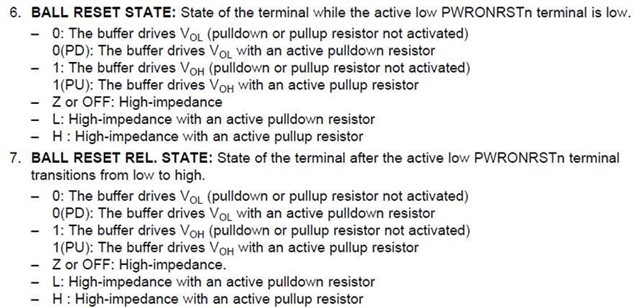

Q1: When AM4378 is in the BALL RESET STATE or BALL RESET REL. STATE listed

in Table 4-10 Pin Attributes in the datasheet, the pull-down/pull-up resistor inside AM4378

and the external pull-up/pull-down resistor are set in intermediate state between them.

Is it a problem that the potential (VILmax to VILmin)?

*After reset is released, the resistors inside AM4378 are released by register setting.

Is there any problem with the intermediate potential since it is described as high impedance

along with pull-down/pull-up resistors in the low or high state as shown below?

Q2. is the intermediate potential during the reset period a problem?

Or is the intermediate potential during the reset period not a problem due to Hi-Z?

My customer's intention is not to intentionally set intermediate potentials,

but to confirm that intermediate potentials due to variations in AM4378, eMMC's

internal pull resistance are not a problem by design.

Best regards,

Kanae