Hi Support Team,

I have received a question from my customer as follows.

*Customer question*

When an eMMC is connected to MMC1 of the CPU, there is a possibility

that an intermediate potential is generated by the internal pull-down (10.58k to 34.61kΩ),

external pull-up resistor (10kΩ) and internal pull-up resistor (10k to 150kΩ) of eMMC

during CPU reset (and immediately after reset release). Is this a problem?

The following is an explanation of the above conditions.

Pull-down resistors inside the CPU

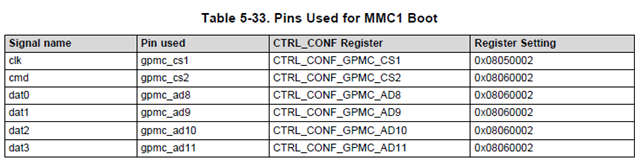

AM437x Technical Reference Manual "5.2.6.5.8 Pins Used" states that

dat0-3 should be assigned to gpmc_ad8, gpmc_ad9, gpmc_ad10 and gpmc_ad11 when Booting MMC1.

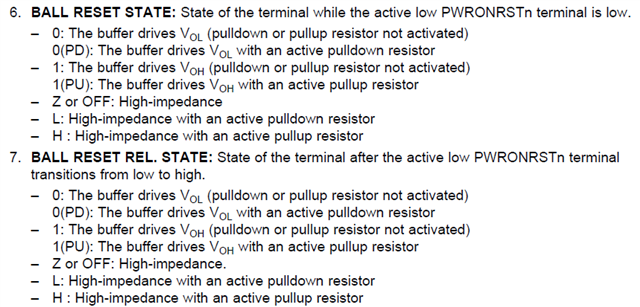

Checking Table 4-10, Pin Attributes in the datasheet, gpmc_ad8, gpmc_ad9, gpmc_ad10,

and gpmc_ad11 have BALL RESET STATE and BALL RESET REL. STATE set to "L" and are pulled down

internally.

-The pull-down resistor values inside the CPU are calculated as follows.

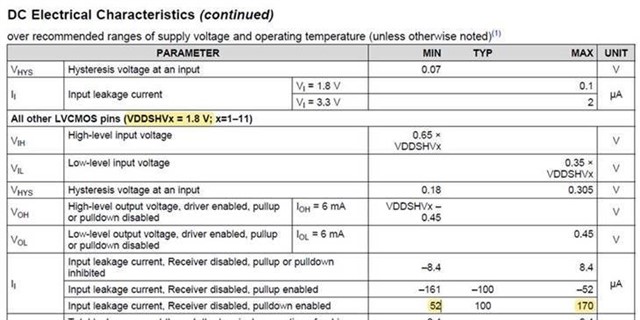

All other LVCMOS pins (VDDSHVx = 1.8 ) with internal resistance valid for Pulldown

VDDSHVx = 1.8

Internal resistance Min. = 1.8V/170μA = 10.58kΩ

Internal resistance Max. = 1.8V/52μA = 34.61kΩ

-External pull-up resistors

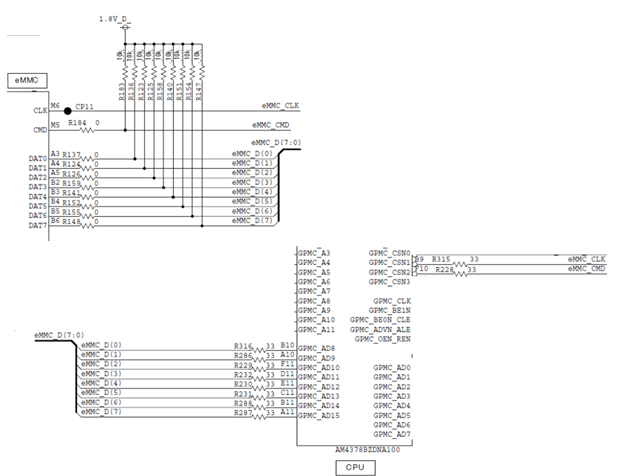

Checking the schematic checklist, there is a section "2.6 MMC" that says

- When connecting a device (card or eMMC), include 10k pullups on RST#, CMD, and all DAT signals.

It is recommended to use external pullups on 10kΩ.

In addition, the JEDEC standard (JESD84-B50) "10.3.4 Bus signal line load"

also lists an external pull-up resistor of 10 to 100kΩ as a requirement for DAT1-7 of eMMC.

-Internal pull-up resistor of eMMC

JEDEC standard (JESD84-B50), "10.3.4 Bus signal line load" states

Internal pull up resistance DAT1-DAT7 is described as 10k to 150kΩ.

If you have unclear points, please let me know.

Best regards,

Kanae