Part Number: TDA4VM

We observed that asymmetric downsample operation fills half of the output with the values from the middle of the layer producing wrong output. I created a small reproducer and attached it.

The example network takes a 1x32x32 input and downscales 2-1 ratio. I attached the reference output from onnx execution with nnef_tools and TIDL PC emulation below. I also attached the network and import/inference configuration in a zip file. The behavior is the same when running on hardware as well.

Input tensor:

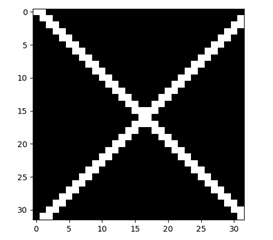

Reference output of neef_tools execution:

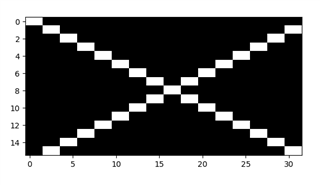

Output of TIDL execution:

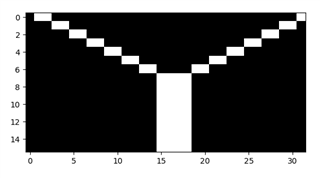

The same happens in width direction as well:

Thanks,

Marton

Importer environment:

Ubuntu 18.04 LTS

SDK: 08_00_00_12