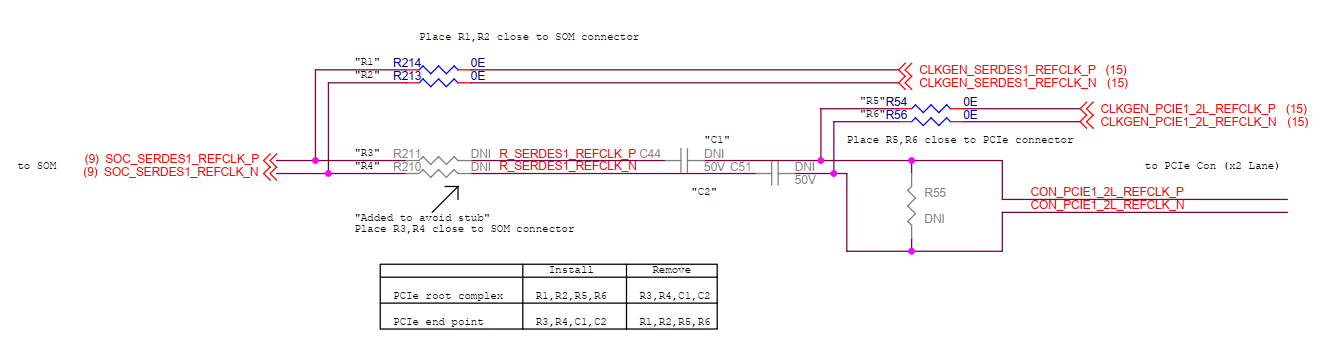

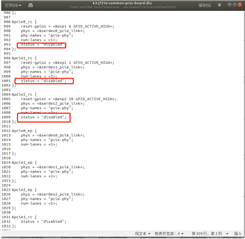

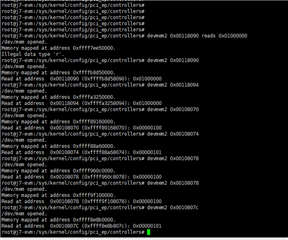

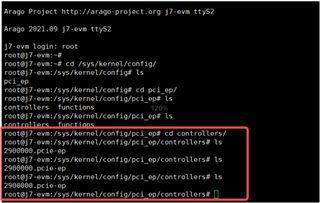

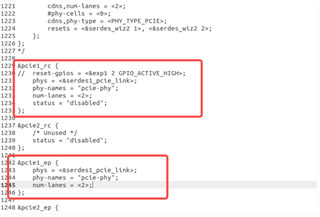

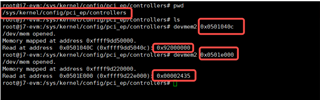

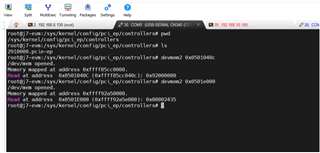

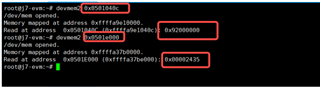

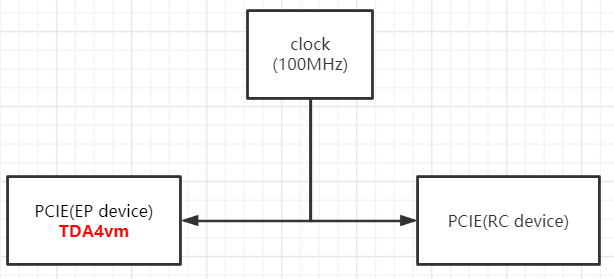

Our design architecture is as follows, we want to use an external clock chip to provide 100MHz clock frequency to PCIE EP and PCIE RC devices at the same time. we use TDA4VM as PCIE EP device in PCIE1 x2 LANE(SERDES1)

my question is :

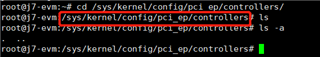

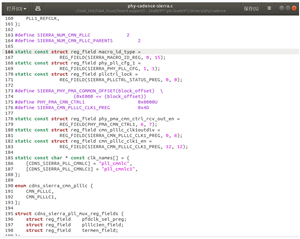

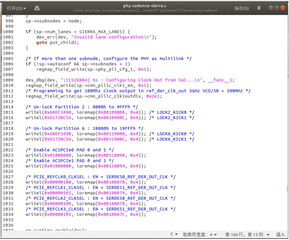

1.When TDA4VM is used as an EP device, does it use an external reference clock by default? If not how to configure it to use an external reference clock?

2.Regarding the hardware connection, we directly connect the output pin of the clock chip to the reference clock pin of SERDES1. But on the EVM board, when used as an EP device, resistors and capacitors are added to the external clock and SERDES1 reference clock pins. Is this necessary?