Part Number: TDA4VM

Hi TI experters,

I'm using LAUTERBACH to debug Mcu Island R5F software based on ti-processor-sdk-rtos-j721e-evm-08_00_00_12.

When boot MCU island R5F cores from NorFlash, i expect the R5F cores will run in lock step mode.

[Observation]:

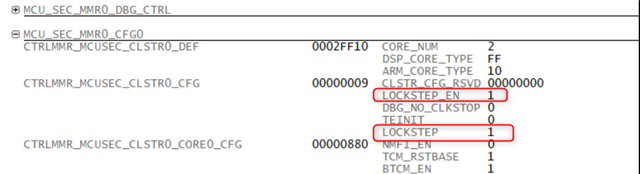

1. When hook in SBL before run SCI services, i see the Mcu Island R5F cores runs lock step mode by observing CTRLMMR_MCUSEC_CLSTR0_CFG

After Mcu Island R5F core requested SCI services, i observed the register CTRLMMR_MCUSEC_CLSTR0_CFG becomes all ZERO.

- seems either its run in split mode ?

- or still run in local step mode but due to some reason the register is not accessible from debugger anymore ?