Part Number: AM6442

Hi,TI team,

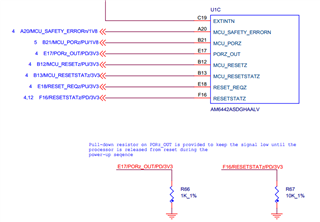

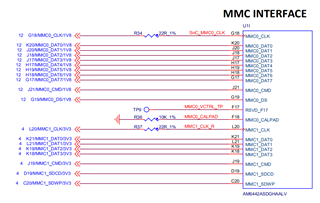

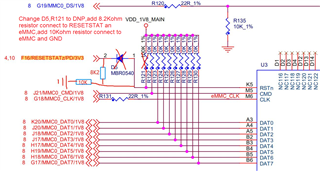

I have a new hardware design on AM6442.

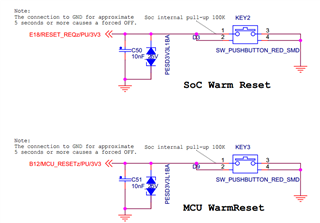

When the hardware boot from SD CARD,I can test the warm reset function controlled by the RESET_REQz HW pin.When the hardware boot from eMMC,I can’t test the warm reset function by the same way.But I can test the warm reset function on TMDS64GPEVM borad whether boot from SD CARD or eMMC.

Then I test the function in u-boot,and use TI XDS200 emulator to connect the A53 core within CCS V11.When RESET_REQz HW pin is triggered while bootting from SD CARD,I found the state of A53 core within CCS like figure 1.

Figure 1

When RESET_REQz HW pin is triggered while bootting from eMMC,I found the state of A53 core within CCS like figure 2.

Figure 2

At this time,I can’t test the reset function whether triggered RESET_REQz HW or MCU_PORZ.

How can I solve this promblem by hardware debug or software debug?

Here are some informations about the new hardware design:

SoC: XAM6442ASFGGAALV SR1.0

DRAM: Micron MT40A1G16RC-062E IT ,2 GiB

eMMC: Skyhigh S40FC004C1B1I00000

U-boot version: U-Boot 2021.01

Thank you in advance.

Best Regards,

Charles Chen