Other Parts Discussed in Thread: CSD,

Tool/software:

Hi TI Experts,

Customer just build their board based on AM64x. Their board does not have SD card, only have eMMC. They are using SDK10.0.

Today they are bringing up their board, and they could use USB-DFU to boot successfully.

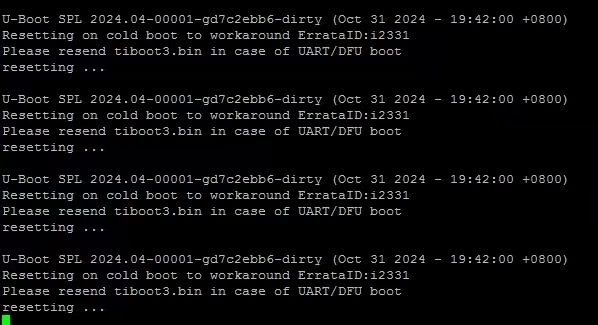

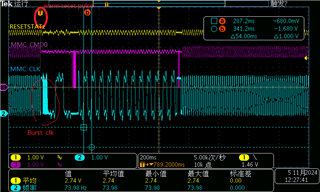

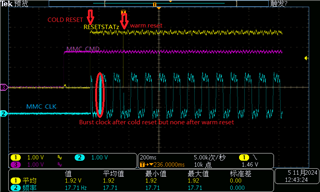

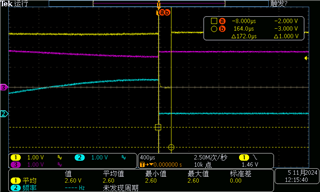

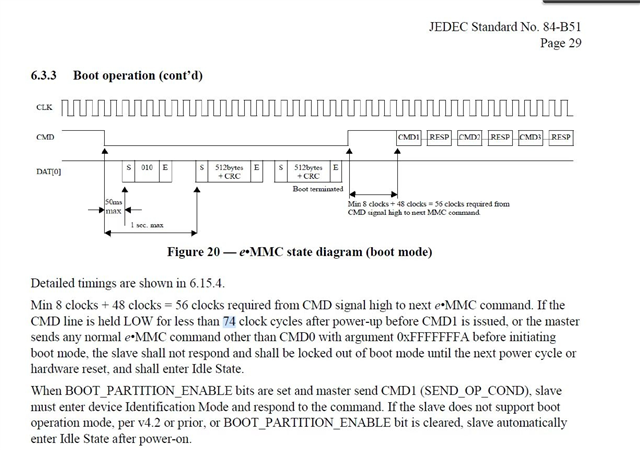

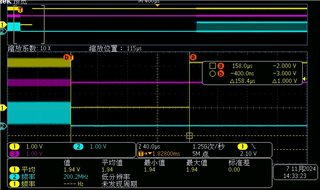

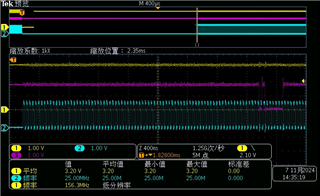

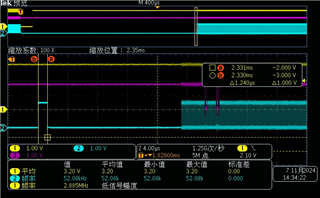

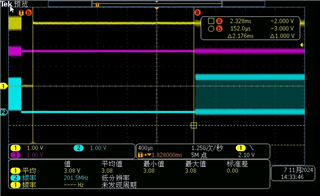

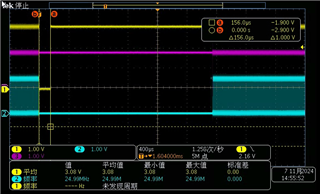

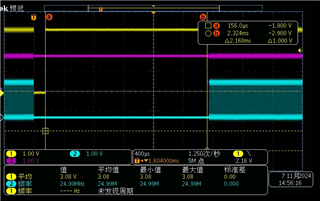

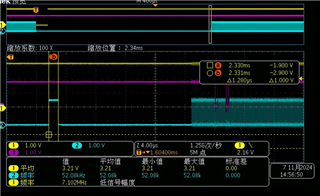

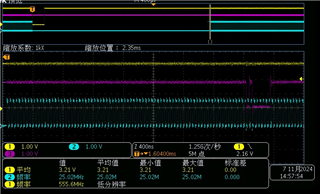

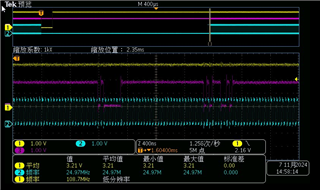

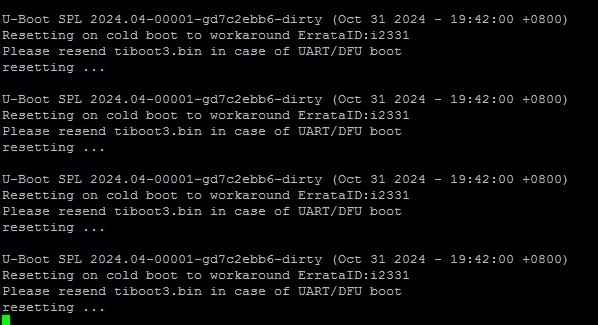

However, when they try on the eMMC boot, they will meet the below problem.

It seems that there is resetting problem, and customer's board will stuck here.

We have found a very similar case below.

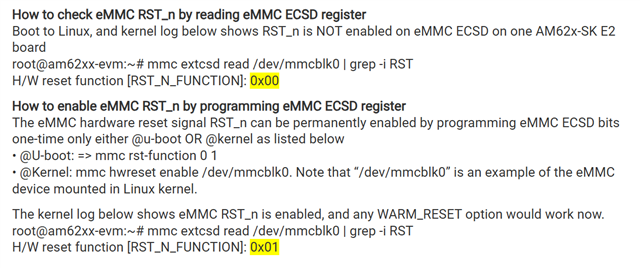

However, after we tried the FAQ mentioned in the above / below link, the problem still exists.

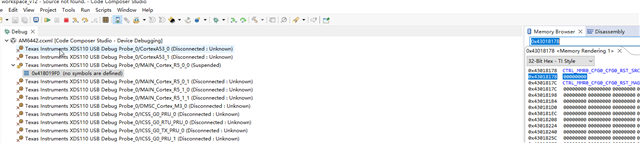

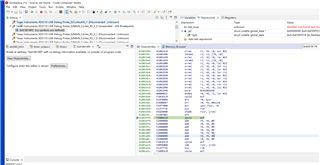

We have tried the below method, but it is not useful.

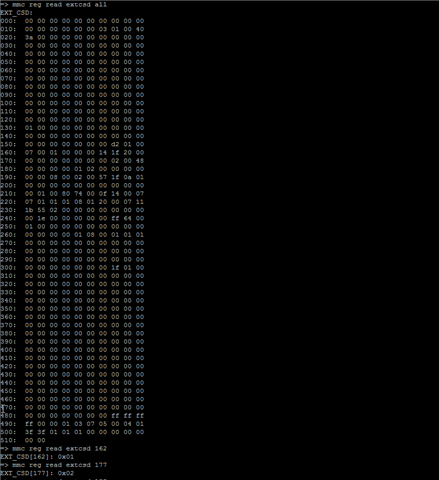

To provide more information for your reference, customer is using 4MB eMMC, our EVM is using 8MB. Customer has followed the below FAQ to modify the code for 4MB eMMC.

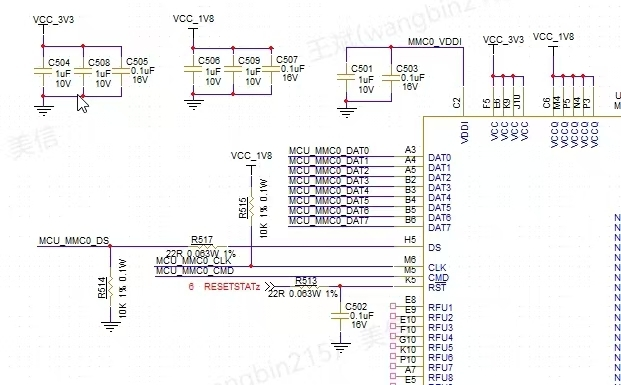

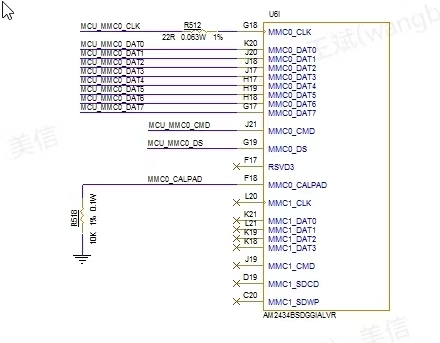

We also doubt that this may also due to the HW design issues, so we also provided the HW schematic for eMMC here for your review.

This is very urgent for customer to bring up the board, and this is a very important project for using AM64x to control multi-axis servo.

Could you please provide some suggestions for customer to try?

Many Thanks,

Kevin