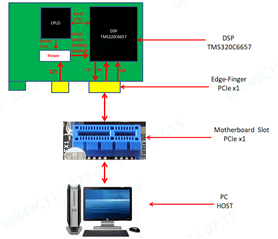

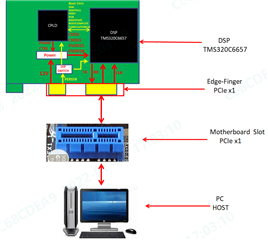

We are designing our customized C6657 board which has PCIe interface connection with PC.

PC works as RC, and DSP as EP.

The board is powered by PCIe slot of PC mother board.

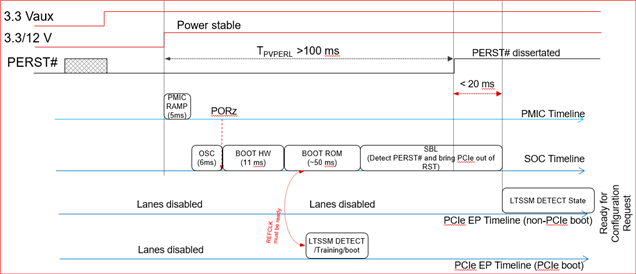

The boot mode is configured as PCIe boot via boot pins.

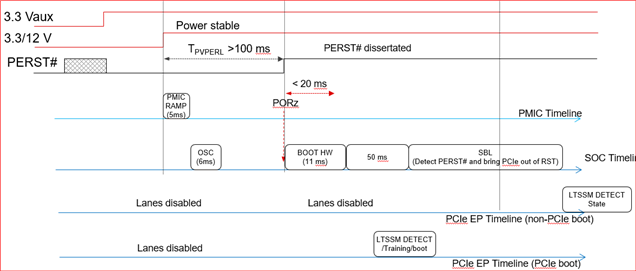

With reference to SPRAC59A PCIe FAQ Section 1.2 - Power Sequencing

The following steps show the power sequencing.

1. PCIe slot on the PC host provides power and reference clock to the PCIe module on the EVM.

2. PCIe boot code on the EVM initializes the C66x PCIe module and waits for the link coming up.

3. PCIe root complex (RC) in the PC host is powered up and a link is established between the PCIe RC in the host and PCIe end point (EP) in the EVM.

4. PC host enumeration (BIOS) starts to scan the PCIe bus.

5. PCIe end point in the EVM is enumerated and registered in the operating system (OS) of the host PC.

My question is: since DSP is powered by mother board, when PC power button is pressed, power will be fed to mother board and DSP at the same time. Then how to guarantee Rom Boot Loader of DSP (Step 2) completes PCIe initialization task before RC power up in PC side (Step 3)?

Any design suggestion?

Thanks.