Hi,

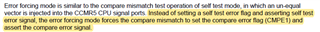

I met a problem when develop the R5F CPU compare block in error forcing mode.

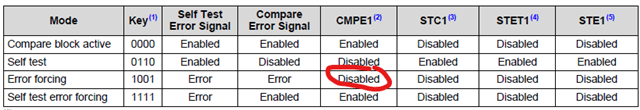

I can't get the register CCMSR.CMPE1 to be set when enter the error forcing mode. Is that because of campare block is disable?

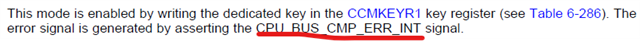

Then, how can I get the error status when enter error focing mode? And where can I found the CPU_BUS_CMP_INT?

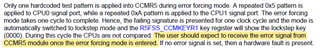

Last, does below sentence mean I can only get the error status in one clock time?

BTW, we are not use the SDL directly, and we have check the code in SDL and can't find the detail information.

If you can give more explaination about that.

Thank you and Best Regards,

Zhihua