- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team AM4,

Ref E2E that was not resolved/finished: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1102863/am4378-pru-and-spi0-nor-flash-pin-mapping-uboot-partitions

My Customer has the following questions..

Our team needs clarification regarding the use of SPI0 NOR Flash. Appreciate your response on this.

Presently we are using SPI0 NOR Flash for booting the board. We are also in need of using PRU ICSSS 0 UART for our serial communication in addition to the other existing UARTS. But this is creating conflicts with the pins where we are looking for swapping SPI0 NOR Flash to some other pins. Here, instead of utilizing default SPI0 pins for NOR Flash where MLO is stored for booting the device, we want to use alternative SPI0 pins (SPI0_CS0; AD25, SPI0_d1; AB25, SPI0_SCLK; AE21) for interfacing the SPI NOR Flash. We want to understand if the Boot ROM can detect the SPI NOR flash if we move the SPI NOR flash to alternative SPI0 pins.

Since we have SPI0 default pins conflicting with PRU ICSS 0, we are also evaluating alternative approach to drop the SPI NOR flash and load MLO in eMMC boot0/boot1 partition. This is not the first FAT partition of the eMMC (FAT32). This is the boot area provided by the eMMC vendor to store the bootloader/boot config data. We want to understand whether the present TI uBoot is supporting boot0/boot1 partitions along with secure boot implementation.

Also, we observed that it takes around 10 to 15 seconds to load the MLO from SPI0 NOR Flash. Is there a way to optimize this?

Our team need a clarification regarding the use of SPI0 NOR Flash. Appreciate your response on this.

Thanks, Merril

*************************************************************************************************************************************************

Brad Caldwell replied..

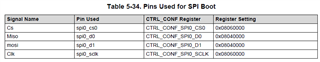

For SPI boot, the ROM code configures the pin-mux registers to use the pins defined in table 5-34 from the TRM shown below. Unfortunately this is hard coded and there aren't any options to change it.

I took a quick look using the sysconfig tool at https://dev.ti.com/sysconfig and you're right, there are direct conflicts with the PRUICSS0 UART pins. I don't see any pin-muxing options to get around this. I did see that PRUICSS1 UART doesn't have conflicts but that of course depends on if you are already using those pins for something else.

I don't think I've seen it done before but perhaps there's a way to boot from SPI0, then later on after boot, reconfigure the pins for PRUICSS0 UART and then at that point use the UART. This would likely require a board change to somehow add an external mux controlled by a GPIO to ensure there's no conflicts between the UART and SPI NOR flash when in one mode or the other.

I'll have to let our Linux experts answer the questions related to eMMC boot but I will say, eMMC is a common way to boot and store your filesystem. I'd first look over the U-Boot documentation in our SDK. The following section describes the eMMC partitioning

*************************************************************************************************************************************************

Hi TI Linux Experts,

Any Update? Additionally the customer asks.. "We are looking forward to the response on our query regarding loading the MLO from eMMC Boot0/Boot1 from TI Boot ROM. Additionally, we also need information for eMMC Boot0/Boot1 partition support available with AM4378 TI U-Boot release. Our recent tests show that the loading of MLO from SPI NOR Flash is taking near to 15 seconds from TI boot ROM on HS boards. However, with SD card, the booting remains normal. So, this puts us to evaluate eMMC as boot device instead of SPI NOR and hence clarifications on our previous questions in this thread is critical. Let us know your response soon."

Thanks, Merril

Hi Merril,

The bootloader booting from memory device (i.e. SPI or eMMC) would be supported by onchip bootrom.

For this reason, the pins connected for memory device are pre-configured by onchip bootrom.

As Brad replied earlier, Pins used by SPI boot is in Table 5-34 of the TRM.

MMC/eMMC boot supported by bootrom are described in 5.2.6.5 MMC/SD Cards of the TRM.

Best,

-Hong