Other Parts Discussed in Thread: SYSCONFIG, DP83869

Our customer wants to use CPSW3g to test TSN on TMDS64GPEVM.

e2e.ti.com/.../am6442-linux-time-sensitive-networking-on-sitara-processors-including-am64x

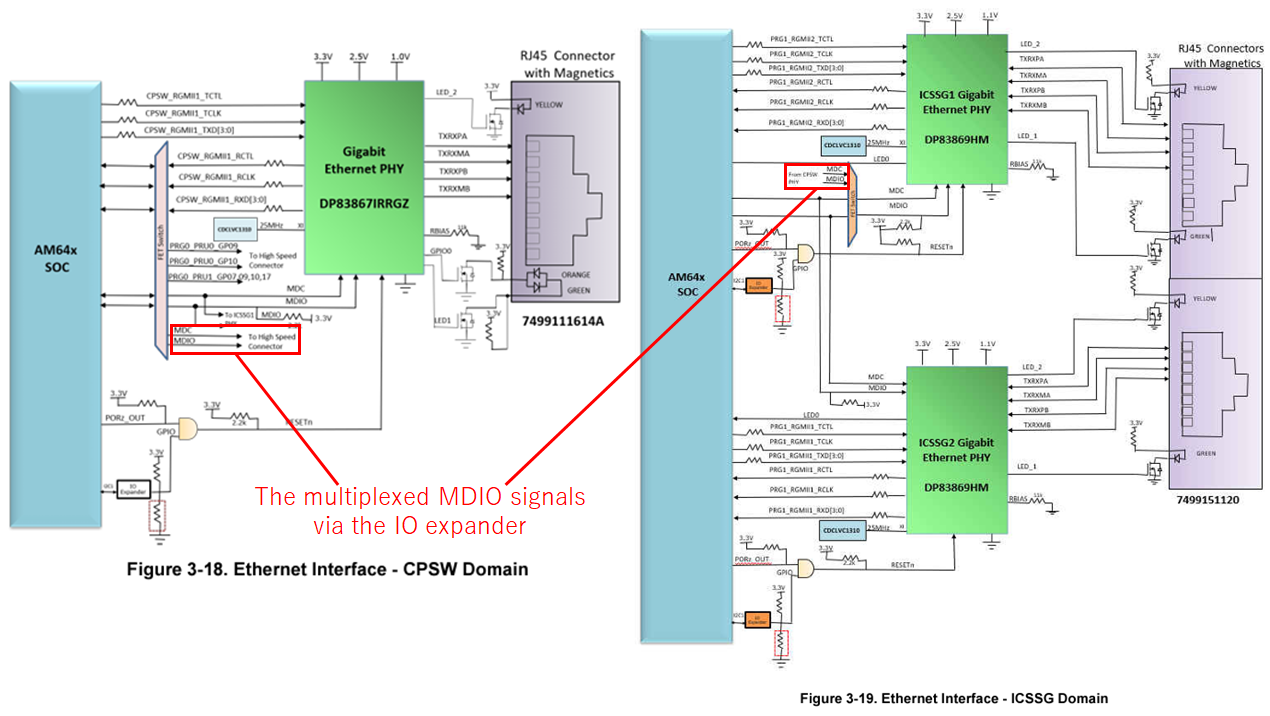

On the TMDS64GPEVM, the CPSW and ICSSG RGMII signals are multiplexed internally, but the MDIO signals are multiplexed via the IO expander, which is controlled by GPIO.

Does the CPSW3g driver in Processor SDK Linux configure the hardware to use CPSW3g instead of ICSSG on the TMDS64GPEVM? In other words, does the driver control GPIO for the multiplexed MDIO?

software-dl.ti.com/.../CPSW3g.html

Best regards,

Daisuke