Environment: DSP C6655,CCS5.5,Win11 64bit

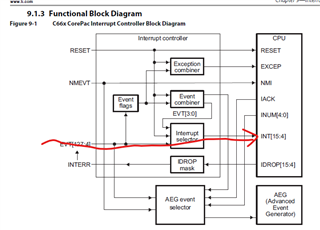

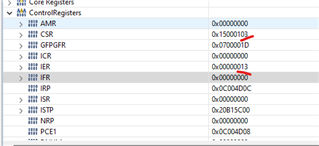

Our objective is to run the EMAC Transmit Completion ISR when the EMAC completes the transmisson of an Ethernet frame. Since the CSL is NOT allowed to be used in my project, therefore, I have to write the code from scratch. EMAC TX INT is routed to CPU INT4, CPU INT4 is set when EMAC completes the transmission. The behavior is correct.

Next step is to request DSP jump into the ISR, I downloaded the vectors.asm from the ticket via the link: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/41441/how-to-initialize-the-interrupt-service-table and copied the modified vectors.asm into my project folder. Please see the code below.

vectors.asm:

.ref _c_int00

.ref _EAMC_TX_Complete

.sect "vectors"

; tell assembler not to use 16-bit compact instructions

; or else the vectors will not reside properly in memory

; (applies to entire section in which it is contained)

.nocmp

RESET_RST:

mvkl .S2 _c_int00, B0

mvkh .S2 _c_int00, B0

B .S2 B0

NOP

NOP

NOP

NOP

NOP

NMI_RST:

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

RESV1:

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

RESV2:

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

INT4:

stw b0,*b15--[2] ; temp save b0 on stack

mvkl _EAMC_TX_Complete,b0 ; load destination address to b0

mvkh _EAMC_TX_Complete,b0

b b0 ; start branch to destination

ldw *++b15[2],b0 ; restore b0 register

nop 2 ; fill 2 of b0 restore delay slots

nop ; fill delay slot, pad packet

nop ; fill delay slot, pad packet

The EAMC_TX_Complete is the ISR and is declared as interrupt void EAMC_TX_Complete(void). The EAMC_TX_Complete function resides in another C source file, not main.c

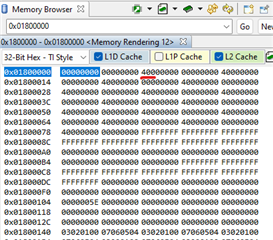

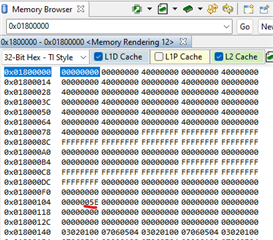

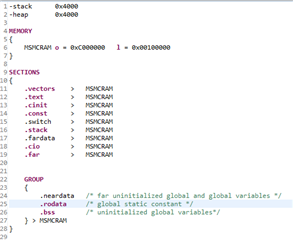

Meanwhile, the cmd file is updated to include the vectors section as shown below.

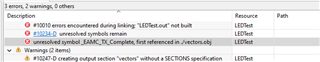

When I compliled the code, the CCS reports errors as shown below.

Questions:

- Is it mandatory to include the lib file called rts66xx.lib? If yes, where can I find out the correct lib file?

- How to address the errors in the Problems field in ccs?

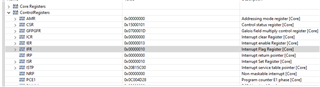

- How to make DSP jump to the ISR once the CPU INT4 is active?

Thanks.