Dear Sitara champs,

About the AM64x supported PTP features

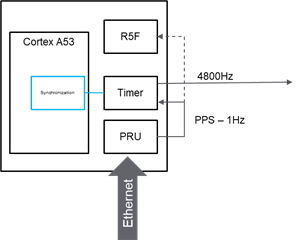

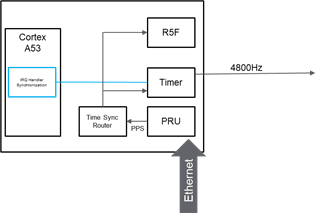

Question 1/ How many PPS signals is it possible to generate through the PRU/CPSW synchronized with PTP clock ?

Question 2/ Is it possible to generate 1Hz and 4800Hz ie 2 signals synchronized with the PTP clock?

In this application the 1Hz signal would be mainly used by internal R5F cores.

Question 3/ So, instead of generating a dedicated output signal, is it possible to generate an IRQ to a specific R5F core ?

This way would save pins by avoiding to generate an output pin signal which will would be connected to an AM64x input pin

Thank you!

Best regards,

Guillaume