Part Number: SK-AM64

Hello,

i saw this forum post:

that pointed to another forum post.

It seems like the original poster didn´t need the answer - but for me, especially question 5 is still relevant:

Quote:

"Question 5:

In several examples, I have seen the following macros for the Write implementation

m_xfr2vbus_write32 .macro xid, addr_low, addr_high

ldi32 r10, addr_low

ldi r11.w0, addr_high

xout xid, &r2, 40

.endm

m_xfr2vbus_write64 .macro xid, addr_low, addr_high

ldi32 r18, addr_low

ldi r19.w0, addr_high

xout xid, &r2, 72

.endm

These macros work perfectly. But if I change the following lines in macros:

m_xfr2vbus_write32: xout xid, &r2, 40 -> xout xid, &r2, 32

m_xfr2vbus_write64: xout xid, &r2, 72 -> xout xid, &r2, 64

they do not work.

Why do I have to specify a length of 40 for 32 bytes to be written and a length of 70 for 64 bytes to be written?

How will the xout command look like to write 1/4/8 bytes of data (What should be the argument length for xout command to write 1/4/8 bytes)? "

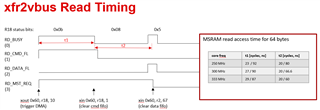

If there is allready further documentation on how to use the XFR2VBUS Hardware Accelerator correctly, i would be happy about a hint. Another question on this topic is:

Is it necessary to use assembly language to use the accelerator effectively?

(Until now i was abled to achieve good results with C-code in PRU projects under CCS 11.1.0 with the PRU C-Compiler v2.3.3)

regards,

Dominik