Hello,

as I need to know the Egress latency and Ingress latency of PRU-ICSSG interfaces and as I was pointed to measure those by myself, I would like to clarify the theoretical operation here, mostly as basis for preparing meaningful measurement process. I am mostly interested in jitter causes and mitigations, as our product is required to have 8 ns timestamp precision at MDI plane.

I have some assumptions and few questions that I would like to clarify. For the assumptions, I would like to ask for confirmation whether those are correct.

Note: Jitter less than 4 ns (as a sum over whole Ingress latency or whole Egress latency) can be considered zero jitter, as it is under the 4 ns resolution of the timestamping clock.

Assumption 1:

Both transmit and receive timestamping is implemented in PRU according to IEEE 802.3 Clause 90.

(I. e. timestamping plane is enter/exit generic reconciliation sublayer of the MAC and message timestamping point is SFD.)

Assumption 2:

Timestamping implementation in PRU uses free running clock counter that is independent on TX_CLK and RX_CLK signals of the xMII interface.

Assumption 3:

When crossing clock domains in PHY, resulting jitter can never be greater than one period of the target clock.

Assumption 4:

Processing in PHY, both sending and receiving, on 10Base-T, 100Base-TX and 1000Base-T (all Full Duplex) have zero jitter (excluding crossing of the clock domains).

Assumption 5:

PCB wiring and magnetics have zero jitter.

Assumption 6:

When transmitting MAC and transmitting PHY share clock signal source, crossing the MAC-PHY clock domain interface has constant latency (zero jitter).

Assumption 7:

When RX_CLK is driven by the line clock (from received data), there is zero added jitter in the PHY processing (thanks to no clock-domain crossing).

Question 1:

Can the PHY, during transmission driven by RGMII (driven by GTX_CLK from PRU) use this clock source for transmission on the medium for 10Base-T Full Duplex, resp. 100Base-TX Full Duplex operation?

(This seems theoretically very well possible at least for 10Base-T, as line clock is not continuous there and receiver clock is always synchronized at the start of the frame, during preamble.)

Question 2:

Can the PHY, during receiving, use link clock to drive the (RG)MII RX_CLK (and the whole decoding process)? If not at all times, what are the conditions when this is/can be done?

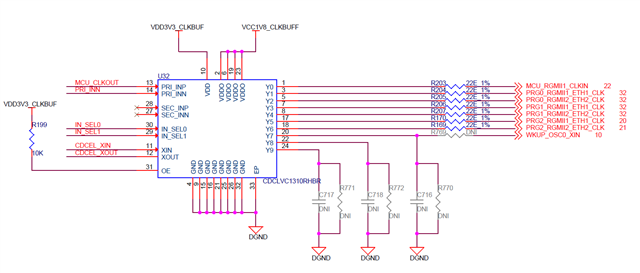

Here I add an illustration of the whole path with Egress latency and Ingress latency marked.

Thanks in advance.

Best Regards,

Jan Smrčina