Part Number: TDA4VM

Dear experts

I ported 100 megabit rmii phy tja1101 on SDK 08_04_00.

Based on gesi module, port4 of cpsw was changed to rmii and all other ports were closed.

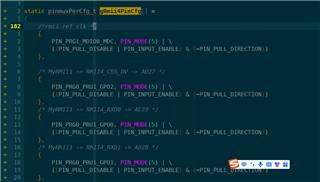

Pinmux of port4 was also changed to rmii.

static Enet_MacPort gEthAppPorts[] =

{

#if defined(SOC_J721E)

/* On J721E EVM to use all 8 ports simultaneously, we use below configuration

RGMII Ports - 1,3,4,8. QSGMII ports - 2,5,6,7

/*ENET_MAC_PORT_1, [> RGMII <]*/

/*ENET_MAC_PORT_3, [> RGMII <]*/

ENET_MAC_PORT_4, /* RGMII */

/*ENET_MAC_PORT_8, [> RGMII <]*/

#if defined(ENABLE_QSGMII_PORTS)

ENET_MAC_PORT_2, /* QSGMII main */

ENET_MAC_PORT_5, /* QSGMII sub */

ENET_MAC_PORT_6, /* QSGMII sub */

ENET_MAC_PORT_7, /* QSGMII sub */

#endif

#elif defined(SOC_J784S4)

ENET_MAC_PORT_1, /* QSGMII main */

ENET_MAC_PORT_3, /* QSGMII sub */

ENET_MAC_PORT_4, /* QSGMII sub */

ENET_MAC_PORT_5, /* QSGMII sub */

#endif

};

static EthFw_VirtPortCfg gEthApp_virtPortCfg[] =

{

{

.remoteCoreId = IPC_MPU1_0,

.portId = ETHREMOTECFG_SWITCH_PORT_0,

},

{

.remoteCoreId = IPC_MPU1_0,

.portId = ETHREMOTECFG_MAC_PORT_4,

},

};

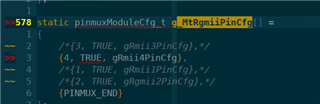

pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_ethernet_config.c

Board_STATUS Board_ethConfigCpsw9g(void)

{

Board_STATUS status = BOARD_SOK;

uint8_t portNum;

/* On J721E EVM to use all 8 ports simultaneously, we use below configuration

RGMII Ports - 1,3,4,8. QSGMII ports - 2 (main),5,6,7 (sub)*/

/* Configures the CPSW9G RGMII ports */

for(portNum=0; portNum < BOARD_CPSW9G_PORT_MAX; portNum++)

{

if ( 0U == portNum ||

2U == portNum ||

3U == portNum ||

7U == portNum )

{

status = Board_cpsw9gEthConfig(portNum, RMII);

}

.....

}

1. The cpsw9g module is initialized properly.

You can see it in the log

Host MAC address: 70:ff:76:1d:92:c3

[LWIPIF_LWIP] Enet LLD netif initialized successfully

[LWIPIF_LWIP_IC] Interface started successfully

[LWIPIF_LWIP_IC] NETIF INIT SUCCESS

[LWIPIF_LWIP_IC] Interface started successfully

[20230103_17:28:20.647][MCU2_0] 13.737601 s: [LWIPIF_LWIP_IC] NETIF INIT SUCCESS

2. The phy register 23 value is 0xbce4. The 15th bit equals 1. That means it's already linked.

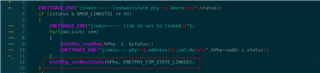

the register 15 value is 0x0080,according to the datasheeet of phy TJA1101,it means PHY can work in mode 100Base-T1. So I configured commonLinkCaps in enetphy.c as ENETPHY_LINK_CAP_FD100; This avoids the "no support caps found".

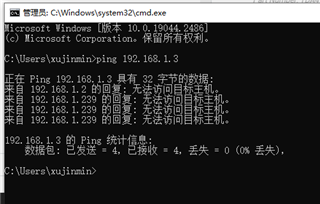

But it is strange that the board cannot ping pc, and the network node is generated. Could please help analyze it, thanks.