Hi Experts:

I using RTOS SDK 07.03 and evm board.

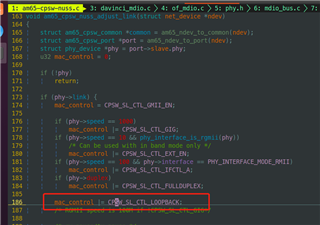

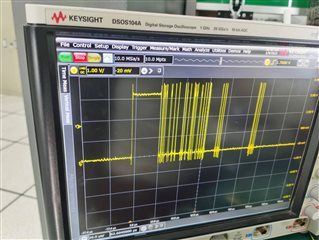

We connect CPSW2G port1 and bcm89836 phy through RMII interface, and configure phy through mdio C45 protocol. Connect the TDA4 board directly to the PC, and find that the PC cannot be pinged. Through ifconifg, it is found that the problem is caused by the absence of rx on the mac. Set mac loopback, ifconfig only has tx, no rx, it should be a problem on the mac side

I turned on mac loopback, and after pinging the PC a few times, the ifconfig is as follows:

The register dump is as follows:

Looking forward to your reply