Other Parts Discussed in Thread: SK-AM62

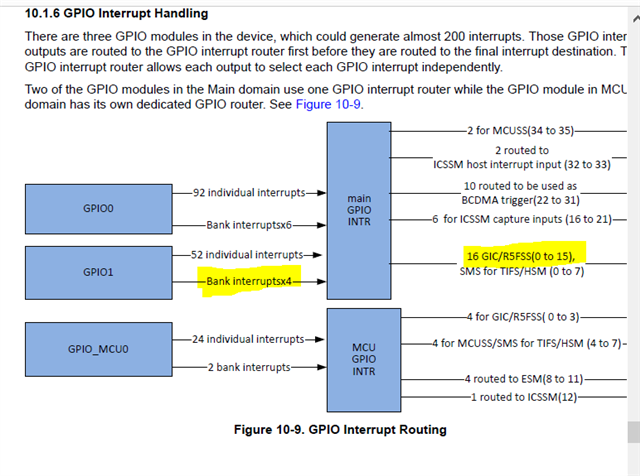

I am attempting to get a design up and going that uses GPIO based interrupts. We are wanting to leverage GPIO1_44-47 as interrupts. I have been referring to two specific examples, but neither seem to work.

The first example that I tried is found in the Processor SDK QNX 08_05_00_0. Specifically it is the psdkqa\qnx\examples\gpio example. When I attempt to port that to our design I am able to build successfully, but the first attempt to write to a GPIO_MUX_BASE_PHY_ADDR register location results in an "Unhandled Exception" error that causes the unit to crash.

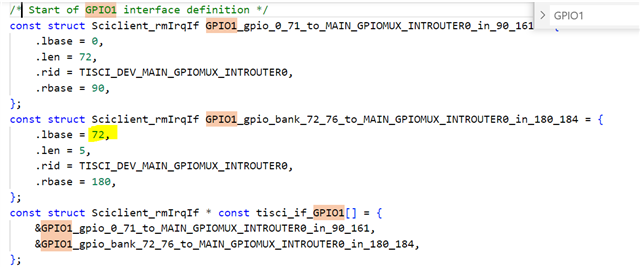

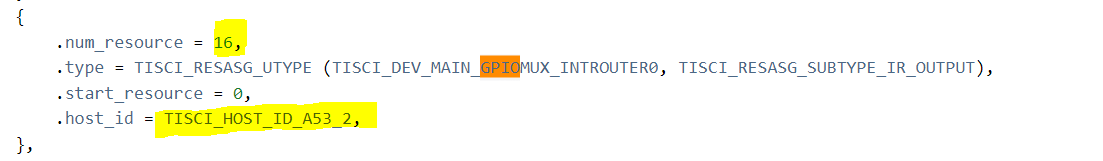

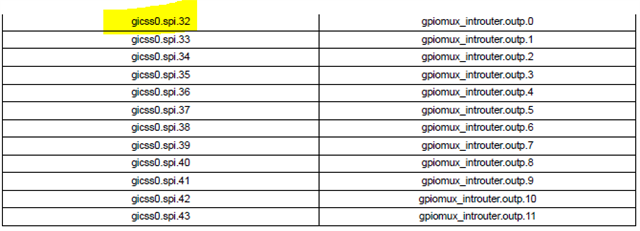

After doing some E2E research, it seemed we might need to use SCI to configure the interrupt router, but it's not clear why that is not the method used for the SDK. Based upon https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1176076/processor-sdk-am62x-gic-interrupts/4469253?tisearch=e2e-sitesearch&keymatch=gpio%25252525252520%25252525252526%25252525252526%25252525252520interrupt#4469253

we have implemented the following code that I think should configure the interrupt router:

static void Sciclient_gpioIrqSet(void)

{

int32_t retVal;

struct tisci_msg_rm_irq_set_req rmIrqReq;

struct tisci_msg_rm_irq_set_resp rmIrqResp;

rmIrqReq.valid_params = 0U;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqReq.global_event = 0U;

rmIrqReq.src_id = TISCI_DEV_MAIN_GPIOMUX_INTROUTER0; //MCU_GPIO_MUX_INT_ROUTER_ID;

rmIrqReq.src_index = 134U;//SRC_IDX_BASE_MCU_GPIO_BANK_0;

rmIrqReq.dst_id = TISCI_DEV_MAIN_GPIOMUX_INTROUTER0; //MCU_GPIO_MUX_INT_ROUTER_ID; // TISCI_DEV_MAIN_GPIOMUX_INTROUTER0 ?

rmIrqReq.dst_host_irq = 32U; //MCU_GPIOMUX_INTROUTER_MCU_0_OUTP_6;

rmIrqReq.ia_id = 0U;

rmIrqReq.vint = 0U;

rmIrqReq.vint_status_bit_index = 0U;

rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSetRaw(&rmIrqReq, &rmIrqResp, -1);

if(0 != retVal)

{

cout << "[Error] Sciclient event config failed!!! RetVal=" << retVal << endl;

//DebugP_log("[Error] Sciclient event config failed!!!\r\n");

//DebugP_assert(FALSE);

}

return;

}

Using this code results in an error message: [Error] Sciclient event config failed!!! RetVal=-1. Further exploration of SLOG shows that every execution of the function results in a new entry in SLOG: Jan 05 18:52:59.587 tisci_mgr.323598 slog 55

ti_sci_msg_xfer (252): sciclient service call failed on ACK

Can someone please direct me towards an example that will work for an AM62x design?

Thanks,

John