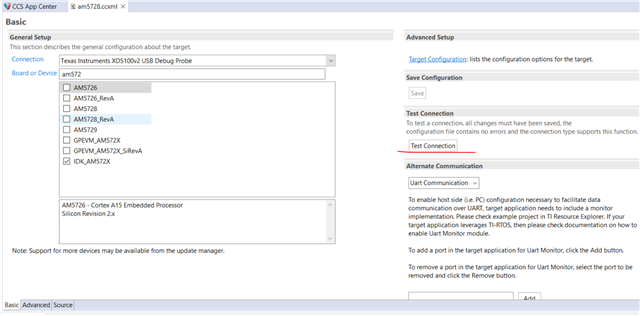

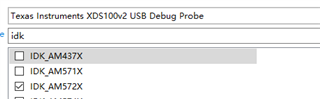

When I connect the target of the idkAM572 board, the compiler complains the following, and the device shut itself off:

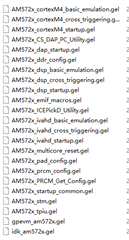

I already confirmed that I use the correct gel file.

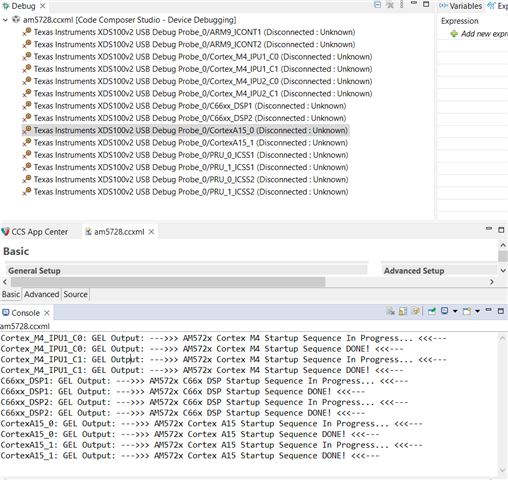

CortexA15_0: Trouble Reading Memory Block at 0x4a005214 on Page 0 of Length 0x4: (Error -1205 @ 0x4A005214) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: GEL: Error while executing OnTargetConnect(): Target failed to read 0x4A005214

at (*((unsigned int*) (base_address+0x04))&0x1) [AM572x_prcm_config.gel:1096]

at dpll_lock_sequence((0x4a005100+0x110)) [AM572x_prcm_config.gel:925]

at dpll_ddr_config(532) [AM572x_ddr_config.gel:1037]

at AM572x_DDR3_532MHz_Config() [AM572x_startup_common.gel:93]

at AM57xx_EVM_Initialization(1) [idk_am572x.gel:54]

at OnTargetConnect()

CortexA15_0: Trouble Reading Register CPSR: (Error -1044 @ 0x3458) The debug probe reported an error. Confirm debug probe configuration and connections, reset the debug probe, and retry the operation. (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register REG_SYSTEM_TARGET_CONFIG: (Error -2131 @ 0x73000000) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register REG_SYSTEM_MMU_CONFIG: (Error -2131 @ 0x73000002) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register REG_SYSTEM_MMU_STATUS: (Error -2131 @ 0x73000003) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register REG_SYSTEM_MMU_STATUS: (Error -2131 @ 0x73000003) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register CP15_Registers.REG_CTXA15_CP15_C2_TTBCR: (Error -2131 @ 0x270F0202) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register CP15_Registers.REG_CTXA15_CP15_C2_TTBR0_64B: (Error -2131 @ 0x278F0020) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register CP15_Registers.REG_CTXA15_CP15_C2_TTBR1_64B: (Error -2131 @ 0x278F1020) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: Trouble Reading Register CP15_Registers.REG_CTXA15_CP15_C3_DACR: (Error -2131 @ 0x270F0300) Unable to access device register. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

CortexA15_0: JTAG Communication Error: (Error -154 @ 0x0) One of the FTDI driver functions used to write data returned bad status or an error. (Emulation package 9.9.0.00040)