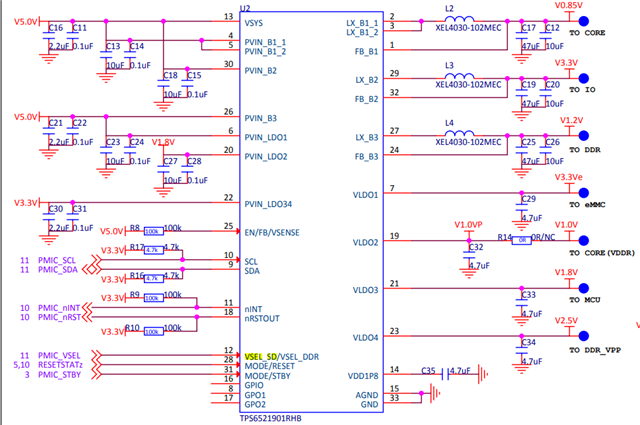

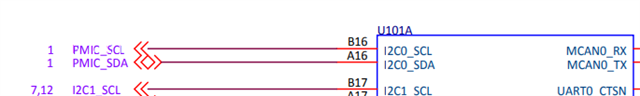

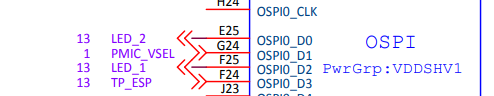

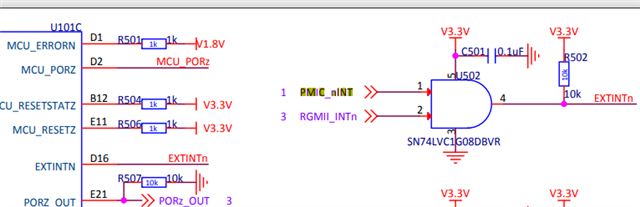

Other Parts Discussed in Thread: SK-AM62, , TPS65219

Hi Team,

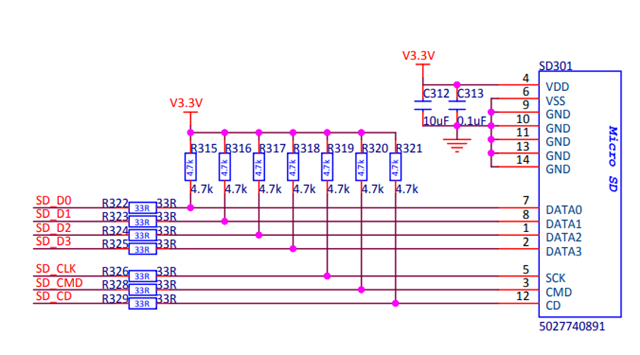

Schematic:

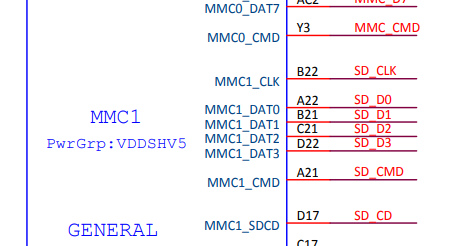

The pins are basically the same, and I use the SD card of SK-AM62 E3 to load content. Could you tell me how to modify the device tree file and uboot configuration?

Kind regards,

Katherine