Other Parts Discussed in Thread: DRA829

HI,

We use a custom DRA829 board.

Linux version is 5.10

SDK is 8.02

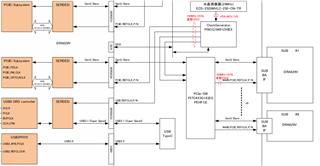

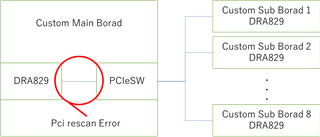

I'm trying to connect a custom board with PCIeSW as RC.

Eight devices are connected to EP of PCIeSW.

PCIeSW releases reset by GPIO after custom board BOOT is finished.

Kernel crashes when PCI rescan is performed after releasing reset.

Attached is the error log and part of the device-tree.

root@j7-evm:/home/root# echo 405 > /sys/class/gpio/export root@j7-evm:/home/root# echo 406 > /sys/class/gpio/export root@j7-evm:/home/root# echo high | tee /sys/class/gpio/gpio406/direction /sys/class/gpio/gpio405/direction high root@j7-evm:/home/root# echo 1 > /sys/bus/pci/devices/0000\:00\:00.0/remove [ 925.440265] pci_generic_config_write32: 21 callbacks suppressed [ 925.440272] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x84 may corrupt adjacent RW1C bits [ 925.455962] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0xdc may corrupt adjacent RW1C bits [ 925.465717] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x92 may corrupt adjacent RW1C bits [ 925.475435] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x9c may corrupt adjacent RW1C bits [ 925.485886] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x92 may corrupt adjacent RW1C bits [ 925.495655] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 925.505371] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 925.515107] pci_bus 0000:01: busn_res: [bus 01] is released root@j7-evm:/home/root# echo 1 > /sys/bus/pci/rescan [ 1000.460264] pci 0000:00:00.0: [104c:b00d] type 01 class 0x060400 [ 1000.466276] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 1000.475924] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 1000.485599] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x92 may corrupt adjacent RW1C bits [ 1000.495328] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0xb2 may corrupt adjacent RW1C bits [ 1000.505083] pci 0000:00:00.0: supports D1 [ 1000.509083] pci 0000:00:00.0: PME# supported from D0 D1 D3hot [ 1000.514820] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x84 may corrupt adjacent RW1C bits [ 1000.525564] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x3e may corrupt adjacent RW1C bits [ 1000.536461] pci 0000:01:00.0: [12d8:c232] type 01 class 0x060400 [ 1000.542961] pci 0000:01:00.0: reg 0x10: [mem 0x00000000-0x0007ffff] [ 1000.549528] pci 0000:01:00.0: PME# supported from D0 D3hot D3cold [ 1000.555755] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0xe8 may corrupt adjacent RW1C bits [ 1000.565701] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0xd0 may corrupt adjacent RW1C bits [ 1000.575483] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0xd0 may corrupt adjacent RW1C bits [ 1000.586087] pci 0000:01:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring [ 1000.595188] pci_bus 0000:02: busn_res: can not insert [bus 02-01] under [bus 01] (conflicts with (null) [bus 01]) ERROR: Unhandled External Abort received on 0x80000000 from S-EL1 ERROR: exception reason=0 syndrome=0xbf000000 Unhandled Exception from EL1 x0 = 0xffff800014610000 x1 = 0x0000000000000000 x2 = 0xffff800014c00008 x3 = 0x0000000000000002 x4 = 0x000000000000000b x5 = 0xffff000803a46800 x6 = 0xffff800012b6f964 x7 = 0x000000000000ea60 x8 = 0x0000000080b5111d x9 = 0x00000000c23212d8 x10 = 0xffff8000111e23a0 x11 = 0xffff8000111fa3e0 x12 = 0x00000000ffffffea x13 = 0xffff0008046df330 x14 = 0x00000000000006b4 x15 = 0xffff0008046dee00 x16 = 0x0000000000000000 x17 = 0x0000000000000000 x18 = 0x0000000000000010 x19 = 0xffff800012b6f8a4 x20 = 0x0000000000000004 x21 = 0xffff000803a44000 x22 = 0x0000000000000087 x23 = 0xffff800012b6f964 x24 = 0x0000000000000000 x25 = 0xffff800011313a98 x26 = 0xffff800010dd31c0 x27 = 0x0000000000000000 x28 = 0x0000000000000000 x29 = 0xffff800012b6f820 x30 = 0xffff8000104f1b3c scr_el3 = 0x000000000000073d sctlr_el3 = 0x0000000030cd183f cptr_el3 = 0x0000000000000000 tcr_el3 = 0x0000000080803520 daif = 0x00000000000002c0 mair_el3 = 0x00000000004404ff spsr_el3 = 0x0000000020000085 elr_el3 = 0xffff8000104f1b54 ttbr0_el3 = 0x0000000070010c00 esr_el3 = 0x00000000bf000000 far_el3 = 0x0000000000000000 spsr_el1 = 0x0000000040000005 elr_el1 = 0xffff8000100b2ec0 spsr_abt = 0x0000000000000000 spsr_und = 0x0000000000000000 spsr_irq = 0x0000000000000000 spsr_fiq = 0x0000000000000000 sctlr_el1 = 0x0000000034d4d91d actlr_el1 = 0x0000000000000000 cpacr_el1 = 0x0000000000300000 csselr_el1 = 0x0000000000000000 sp_el1 = 0xffff800012b6f820 esr_el1 = 0x0000000056000000 ttbr0_el1 = 0x00000008819b4600 ttbr1_el1 = 0x0a80000082f50000 mair_el1 = 0x000c0400bb44ffff amair_el1 = 0x0000000000000000 tcr_el1 = 0x00000034f5d07590 tpidr_el1 = 0xffff80086eab0000 tpidr_el0 = 0x0000ffffac503c40 tpidrro_el0 = 0x0000000000000000 par_el1 = 0x0000000000000000 mpidr_el1 = 0x0000000080000000 afsr0_el1 = 0x0000000000000000 afsr1_el1 = 0x0000000000000000 contextidr_el1 = 0x0000000000000000 vbar_el1 = 0xffff800010010800 cntp_ctl_el0 = 0x0000000000000005 cntp_cval_el0 = 0x0000002ed234d87d cntv_ctl_el0 = 0x0000000000000000 cntv_cval_el0 = 0x0000000000000000 cntkctl_el1 = 0x00000000000000d6 sp_el0 = 0x000000007000a3d0 isr_el1 = 0x0000000000000040 dacr32_el2 = 0x0000000000000000 ifsr32_el2 = 0x0000000000000000 cpuectlr_el1 = 0x0000001b00000040 cpumerrsr_el1 = 0x0000000000000000 l2merrsr_el1 = 0x0000000000000000

arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

pcie0_rc: pcie@2900000 {

compatible = "ti,j721e-pcie-host";

reg = <0x00 0x02900000 0x00 0x1000>,

<0x00 0x02907000 0x00 0x400>,

<0x00 0x0d000000 0x00 0x00800000>,

<0x00 0x10000000 0x00 0x00001000>;

reg-names = "intd_cfg", "user_cfg", "reg", "cfg";

interrupt-names = "link_state";

interrupts = <GIC_SPI 318 IRQ_TYPE_EDGE_RISING>;

device_type = "pci";

ti,syscon-pcie-ctrl = <&scm_conf 0x4070>;

max-link-speed = <3>;

num-lanes = <2>;

power-domains = <&k3_pds 239 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 239 1>;

clock-names = "fck";

#address-cells = <3>;

#size-cells = <2>;

bus-range = <0x0 0xff>;

vendor-id = <0x104c>;

device-id = <0xb00d>;

msi-map = <0x0 &gic_its 0x0 0x10000>;

dma-coherent;

ranges = <0x01000000 0x0 0x10001000 0x0 0x10001000 0x0 0x0010000>,

<0x02000000 0x0 0x10011000 0x0 0x10011000 0x0 0x7fef000>;

dma-ranges = <0x02000000 0x0 0x0 0x0 0x0 0x10000 0x0>;

#interrupt-cells = <1>;

interrupt-map-mask = <0 0 0 7>;

interrupt-map = <0 0 0 1 &pcie0_intc 0>, /* INT A */

<0 0 0 2 &pcie0_intc 0>, /* INT B */

<0 0 0 3 &pcie0_intc 0>, /* INT C */

<0 0 0 4 &pcie0_intc 0>; /* INT D */

pcie0_intc: interrupt-controller {

interrupt-controller;

#interrupt-cells = <1>;

interrupt-parent = <&gic500>;

interrupts = <GIC_SPI 312 IRQ_TYPE_EDGE_RISING>;

};

};

arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

&pcie0_rc {

phys = <&serdes0_pcie_link>;

phy-names = "pcie-phy";

num-lanes = <2>;

};

Please give me a solution or advice.