Other Parts Discussed in Thread: SK-AM62

Hello,

I have some questions about how the UDMA works and about the UDMA API provided by TI in the PSDK. My ultimate goal is to use DMA to transfer data from GPMC_DATA to RAM which gets kicked off by an interrupt from GPIO. I've studied and ran the qnx/examples/udma/udma_memcpy_test_qnx/src/udma_memcpy_test.c which works on our hardware with no modifications, but I have some questions:

- In App_udmaTrpdInit I notice the example is using transfer record type 15, do you know why this type was used compared to transfer record type 11? Reading the reference manual I see the additional loops provides additional places for an event to stall the DMA transfer, but I don't see that happening in this example. What scenarios would software want to stall the transfer? Is there another reason to want to use multiple loops as shown in section 11.1.3.3.2.1.

- I'm having trouble finding information about FMTFLAGS, can you point me to where in the reference manual this is described?

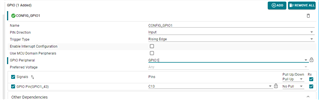

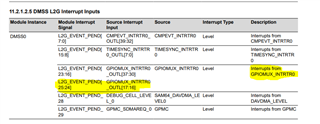

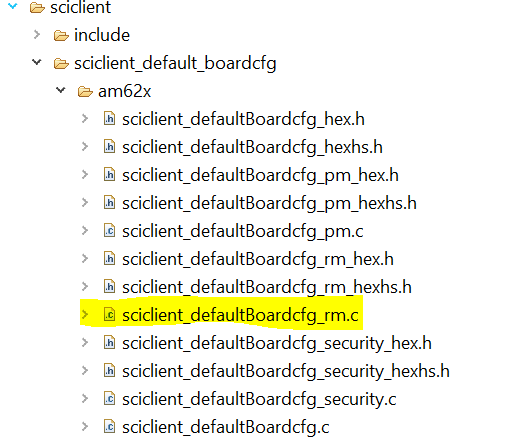

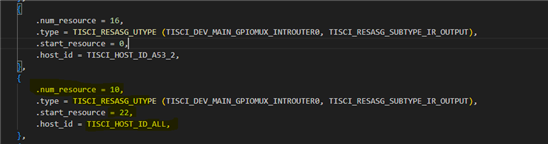

- For interrupts, I want to check my understanding of how I should set up TISCI. I will use TISCI to set valid_parms to TISCI_MSG_VALUE_RM_IA_ID_VALID | TISCI_MSG_VALUE_RM_VINT_VALID | TISCI_MSG_VALUE_RM_GLOBAL_EVENT_VALID | TISCI_MSG_VALUE_RM_VINT_STATUS_BIT_INDEX_VALID as per the chart on the TISCI website here https://software-dl.ti.com/tisci/esd/latest/2_tisci_msgs/rm/rm_irq.html#pub-rm-irq-route-set. To understand what each of the various settings should be I referred to https://software-dl.ti.com/tisci/esd/latest/5_soc_doc/am62x/interrupt_cfg.html#interrupt-aggregator-device-ids.

- ia_id should be 28

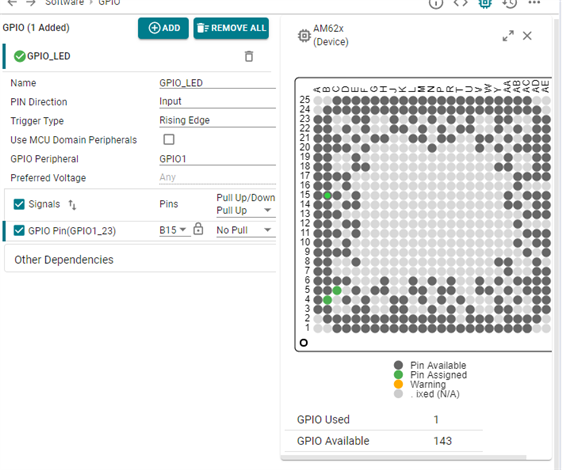

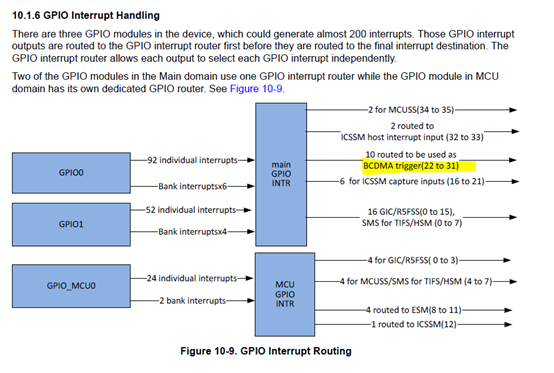

- vint should be one of the IA VINT Index values that correspond to a GICSS0 destination since I'm using GPIO to trigger the interrupt

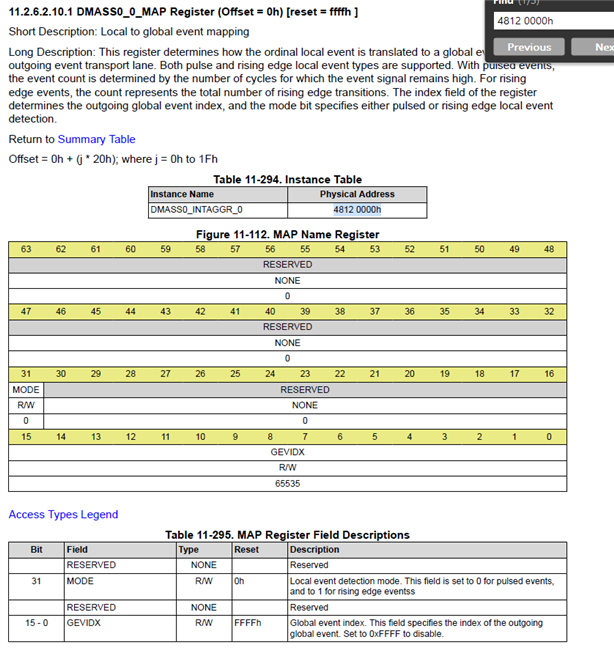

- global_event - Can you confirm that this should be one of the BCDMA_0 Trigger indexes in the range of 50176 to 50339? Considering I want this interrupt to trigger a BCDMA this seems like the range.

- vint_status_bit_index - Can you explain this field and how it's used?

- Once I use TISCI to configure the interrupt, I believe I need to modify the transfer request so it triggers on either on CSL_UDMAP_TR_FLAGS_TRIGGER_GLOBAL0 or CSL_UDMAP_TR_FLAGS_TRIGGER_GLOBAL1, can you explain the difference between these two triggers?

- I believe that when I set up the UDMA events, I need to configure the eventType = UDMA_EVENT_TYPE_TR, make the event exclusive, and set vintrNum to the global_event I entered when configuring the interrupt. Can you confirm that my understanding is correct? Will I still be able to set the eventCb?

- One more item, when I changed the source buffer from pointing to a virtual address in RAM to the virtual address that QNX maps the physical address of GPMC_DATA (0x50000000) and run the example, I see that the first 4 bytes are copied correctly, but the others do not. Is this a symptom of how the transfer record is set or do I need to refer to how the GPMC_CFG register is set up to configure the DMA?

-

Source Buffer virtual=0x3dd6985000(phys=0x50000000):

src[0] = 0x50504502

src[1] = 0x00

src[2] = 0x9ECCFDBF

src[3] = 0xFFFFFFFF

-

Destination Buffer virtual=0x3dd6984000(phys=0xbf06c000):

dst[0] = 0x50504502

dst[1] = 0x50505050

dst[2] = 0x50505050

dst[3] = 0x50505050

-

Thank you very much for your help!

From,

Daniel Fettke