I'm extremely confused due to small inconsistencies in the docs. Please clarify on these various clocks for me and update the docs accordingly.

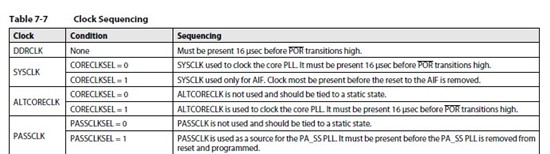

In the diagram above there is something called "Core PLL" and it has signals SYSCLKP/N feeding into it through a mux.

There is no signal in the data sheet called SYSCLKP or SYSCLKN, nor is there anything called "Core PLL".

>> So are SYSCLKP/N intended to be CORECLKP/N? That's my assumption...

>> Is "Core PLL" actually referring to "Main PLL" as described in the data sheet?

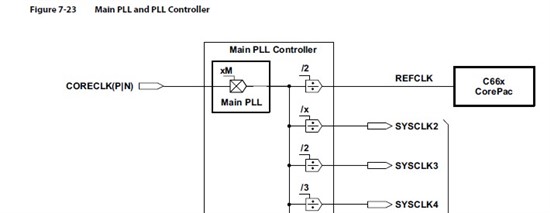

In the snippet above we see references to SYSCLK and "core PLL" again. The closest diagram I can find to clarify is this one:

However, in the above diagram we are use the terminology "CORECLK" and "Main PLL", but I do not even see the mux for CORECLKSEL as described in the previous documentation. So now I'm wondering if these are even referring to the same thing?

Can someone please clarify on the clock diagrams?