Hi TI Experts,

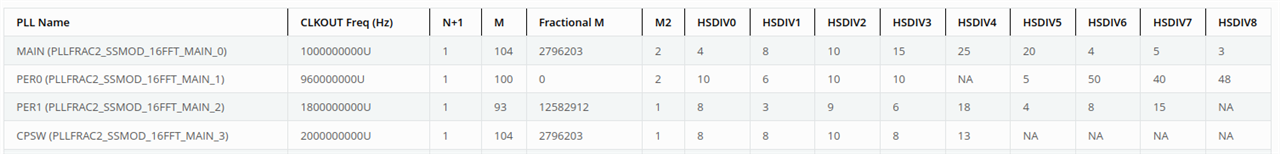

Customer is trying to adjust the CPTS reference clock frequency: DEV_NASS0_CPTS_0_RCLK. They want it to be at 1Ghz.

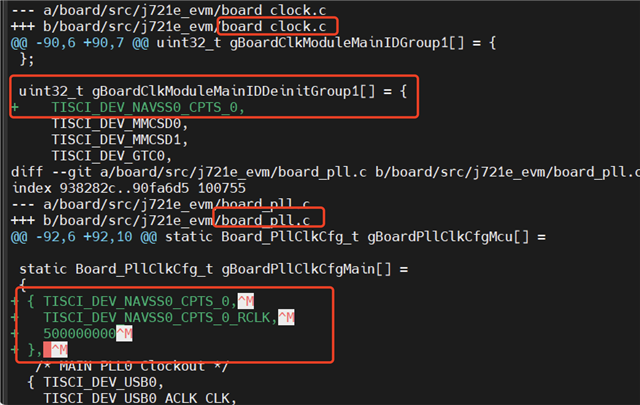

However, they have added the corresponding configuration of CPTS in both board_pll.c & board_clock.c in SBL shown below, but it does not work.

Could you help on this to see if any other places need to be changed to adjust DEV_NASS0_CPTS_0_RCLK frequency?

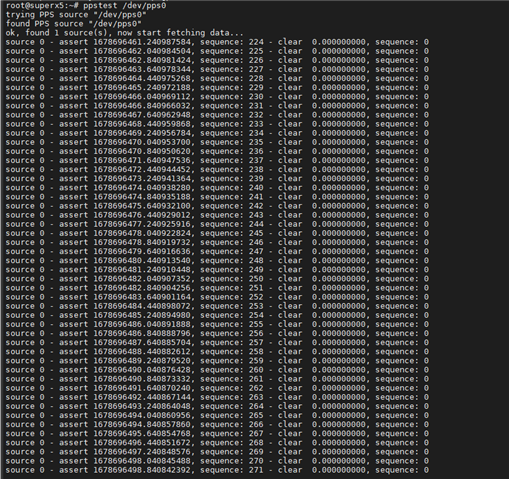

Another question is that customer finds ppstest time stamp result mismatches with the clock frequency.

Firstly, they have created /dev/pps0 successfully from the below link.

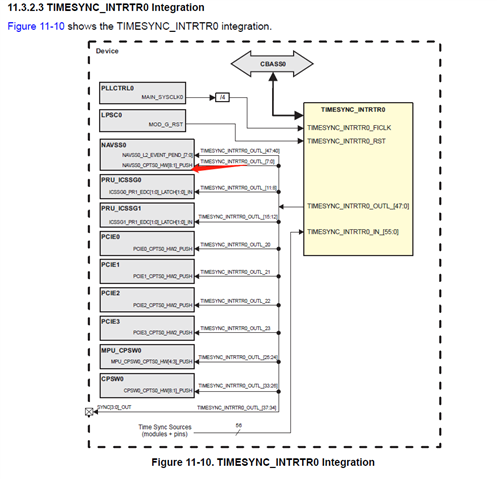

They are using HWITSPUSHIN as input & NAVSS0 HW8_TS_PUS as output

However, from the ppstest result, the time interval is around 0.8s not equal to expected 1s.

Could you provide some feedback & suggestions about it?

Kind Regards,

Kevin