Other Parts Discussed in Thread: DRA829

Hi,

Since the following thread was locked, let me post another thread.

DRA829V: How can we change the peripheral value to 80 (QSPI) of Boot Parameter Table Common Header

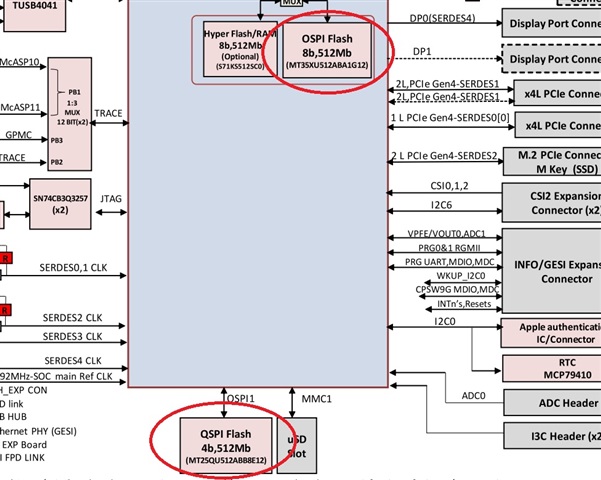

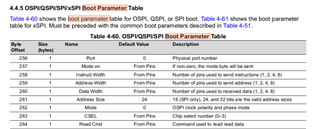

As mentioned in the above thread, the customer set the BOOT pins as QSPI boot, and QSPI boot was done successfully. However, "Peripheral" was set as "85" OSPI, not "80" QSPI in the Boot Parameter Table Common Header described in the Table 4-51. in the page 1052 of DRA829 TRM.

Why is it ? How can they set it as QSPI "80" correctly ?

Regards,

Hideaki