Other Parts Discussed in Thread: TDA4VH,

Hi,

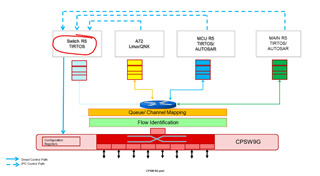

my customer has a couple of questions regarding TSN (Time-Sensitive Networking) features for TDA4VM and TDA4VH:

- Is there any documentation available for using and configuring TSN on QNX, Linux and FreeRTOS?

- Are there any examples for TSN within the SDK for TDA4VM?

- Could you please provide us with a roadmap for TSN features?

- Does TSN features supported on CPSW9G in TDA4VH is same for the TDA4VM?

Regards,

Jon