Other Parts Discussed in Thread: TDA4VM, TDA4VL

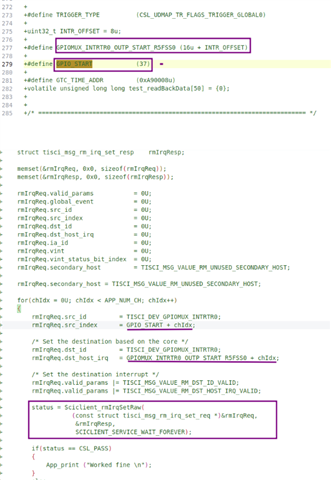

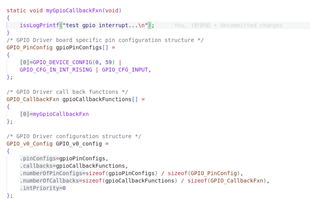

I want to set gpio0_59 interrupt on the muc2_0, the following is the setup process,

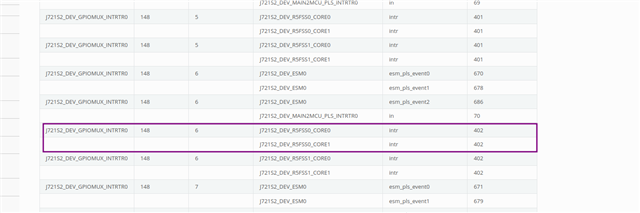

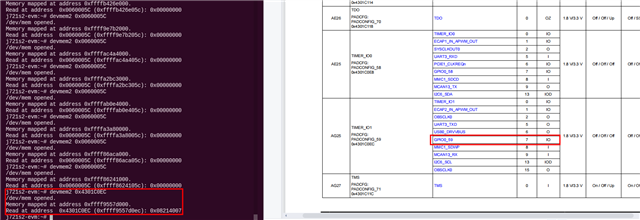

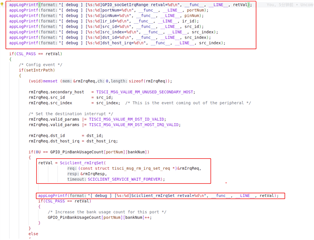

but the break registration process is under ti-processor-sdk-rtos-j721s2-evm-08_06_00_11/pdk_j721s2_08_06_00_31/packages/ti/drv/gpio/soc/j721s2/GPIO_soc.c GPIO_ socConfigIntrPath returns -1,

I added a print trace under this function, and found that calling the Sciclient_rmIrqSet function failed,

I don't know why the call is unsuccessful, can you give a suggestion, thank you