Part Number: AM625

Hi,

Our custom board will use UART4 as a serial console.

Since the board is not yet complete, we are experimenting with AM62x-SK EVM.

We have modified the DTS of the U-Boot as follows:

diff --git a/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common-u-boot.dtsi b/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common-u-boot.dtsi

index b57d9563d87..51397bfdfdd 100644

--- a/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common-u-boot.dtsi

+++ b/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common-u-boot.dtsi

@@ -68,11 +68,11 @@

u-boot,dm-spl;

};

-&main_uart0 {

+&main_uart4 {

u-boot,dm-spl;

};

-&main_uart0_pins_default {

+&main_uart4_pins_default {

u-boot,dm-spl;

};

diff --git a/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common.dtsi b/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common.dtsi

index fd52bb2872e..a899b8394ea 100644

--- a/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common.dtsi

+++ b/sdk/u-boot/arch/arm/dts/k3-am62x-sk-common.dtsi

@@ -14,7 +14,7 @@

/ {

aliases {

- serial2 = &main_uart0;

+ serial2 = &main_uart4;

mmc0 = &sdhci0;

mmc1 = &sdhci1;

mmc2 = &sdhci2;

@@ -141,10 +141,10 @@

};

&main_pmx0 {

- main_uart0_pins_default: main-uart0-pins-default {

+ main_uart4_pins_default: main-uart4-pins-default {

pinctrl-single,pins = <

- AM62X_IOPAD(0x1c8, PIN_INPUT, 0) /* (D14) UART0_RXD */

- AM62X_IOPAD(0x1cc, PIN_OUTPUT, 0) /* (E14) UART0_TXD */

+ AM62X_IOPAD(0x0124, PIN_INPUT, 3) /* (A23) MMC2_SDCD.UART4_RXD */

+ AM62X_IOPAD(0x0128, PIN_OUTPUT, 3) /* (B23) MMC2_SDWP.UART4_TXD */

>;

};

@@ -273,8 +273,7 @@

};

&main_uart0 {

- pinctrl-names = "default";

- pinctrl-0 = <&main_uart0_pins_default>;

+ status = "disabled";

};

&main_uart1 {

@@ -291,7 +290,8 @@

};

&main_uart4 {

- status = "disabled";

+ pinctrl-names = "default";

+ pinctrl-0 = <&main_uart4_pins_default>;

};

&main_uart5 {

Then, a panic has occurred at serial_find_console_or_panic() in R5 SPL.

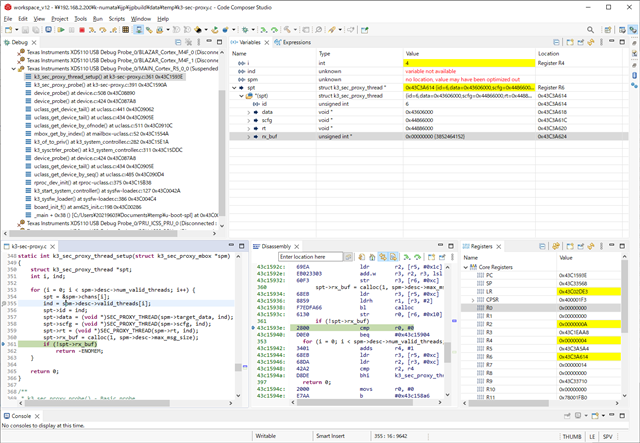

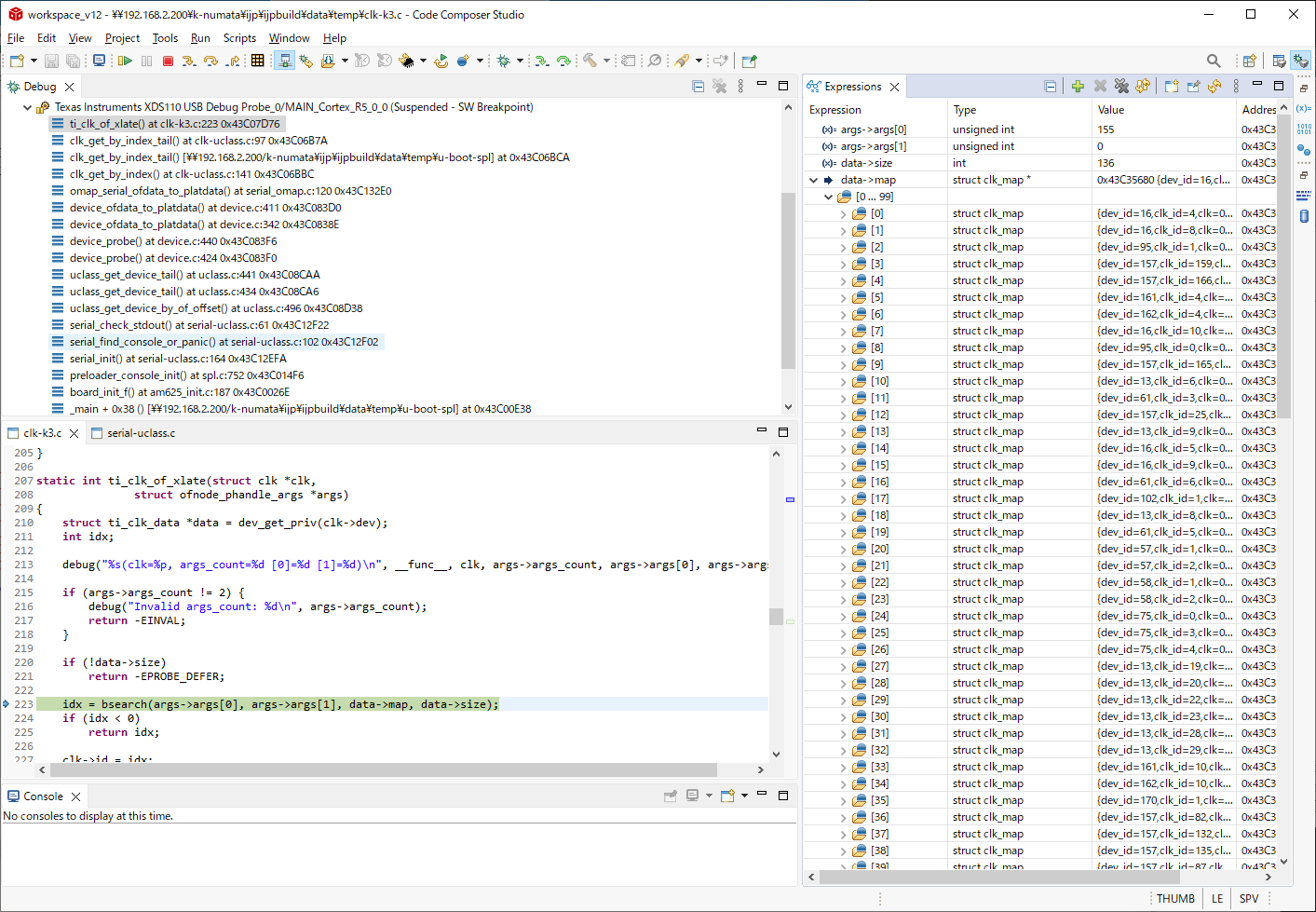

The cause seems to be that ti_clk_of_xlate() is returning an error.

In arch/arm/dts/k3-am65-main.dtsi, UART0 and UART4 are defined as follows:

main_uart0: serial@2800000 {

compatible = "ti,am64-uart", "ti,am654-uart";

reg = <0x00 0x02800000 0x00 0x100>;

interrupts = <GIC_SPI 178 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 146 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 146 0>;

clock-names = "fclk";

};

...

main_uart4: serial@2840000 {

compatible = "ti,am64-uart", "ti,am654-uart";

reg = <0x00 0x02840000 0x00 0x100>;

interrupts = <GIC_SPI 182 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 155 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 155 0>;

clock-names = "fclk";

};

We assume that the error is caused because the definition corresponding to clocks = <&k3_clks 155 0> does not exist in arch/arm/mach-k3/am62x/clk-data.c.

static const struct dev_clk soc_dev_clk_data[] = {

...

DEV_CLK(146, 0, "main_usart0_fclk_sel_out0"),

DEV_CLK(146, 1, "usart_programmable_clock_divider_out0"),

DEV_CLK(146, 2, "hsdiv4_16fft_main_1_hsdivout1_clk"),

DEV_CLK(146, 5, "sam62_pll_ctrl_wrap_main_0_chip_div1_clk_clk"),

...

}

Could you please advise how to fix this problem?