Other Parts Discussed in Thread: AM625, AM623, AM625-Q1, AM620-Q1, SYSCONFIG

I have a SK-AM62 E3A

I am compiling my own custom yocto linux build using meta-ti.

meta-ti version: b86456651b1b9ce1e0612f9892387ec54b4f5759, tag: 09.00.00.004

linux version: 2b6f5746de558d954e42749b898fcdb4227dce5a, tag: 09.00.00.004

I am seeing this relevant commit message:

commit f608d07b036dee9529e93e49d7767b5affbf5353

Author: Siddharth Vadapalli <s-vadapalli@ti.com>

Date: Mon May 29 10:00:03 2023 +0530

arm64: dts: ti: k3-am625-sk: Add CPSW3G CPTS PPS supportAnd I am seeing these links:

[0] Link: software-dl.ti.com/.../interrupt_cfg.html [1] Link: software-dl.ti.com/.../interrupt_cfg.html

But I still cannot figure out what I can do to identify a specific pin that will output the PPS so that I can measure it.

Can someone help me understand what I can do?

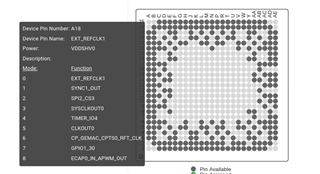

I have tried locating cpts_hw3_push on the ti pinmux tool after selecting am62x device and alw package, but I can't find it.