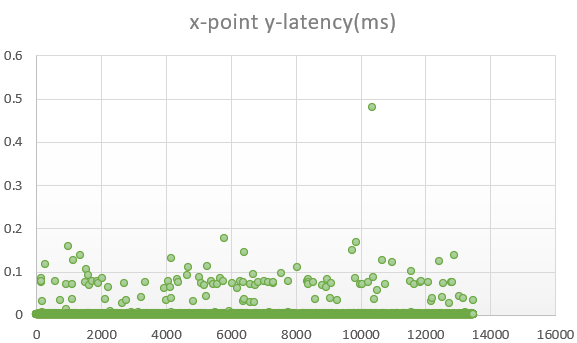

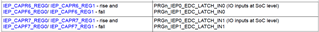

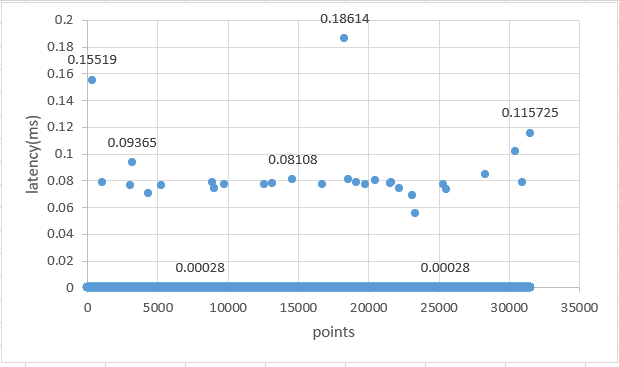

I want to test the communication latency through rpmsg between A53 and PRUs, so I want to record the timestamp when A53 sends message to PRU and the timestamp when PRU receives the message. Can you share the example of using IEP timer to get the current counter value? And how can I make sure that this IEP timer counter is synced with system time?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.