Hell Ti ,

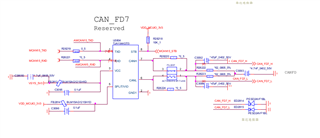

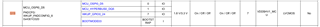

Configure can7 as follows,can7 can only receive a signal once, and after that, there will be no human signal or waveform. Could you please help confirm what can7 should be configured according to? thanks. The following is the configuration of can7.

Current status:

Phenomenon: After being powered on, there was a data transmission signal, and then it disappeared;

We configure PINMUX related information in the code according to MCAN15;

MCAN15_ The voltage of the STB PIN pin has been lowered and entered the working mode, and the voltage has not been raised after entering the working mode;