Part Number: TDA4VM

We want to execute PBIST and LBIST in MCU, so change the file below.

psdkra/mcusw/mcuss_demos/boot_app_mcu_rtos/makefile

BISTFUNC ?= enabled

And turn on the debug macro .

But something wrong .

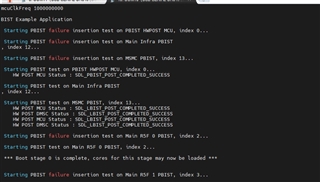

Log:

For HW POST LBIST core 0, Expected MISR= 0xe851b017, Calculated MISR = 0xe851b017

HW POST core: HWPOST - DMSC: result = 0

For HW POST LBIST core 1, Expected MISR= 0x296b47db, Calculated MISR = 0x296b47db

HW POST core: HWPOST - MCU: result = 0

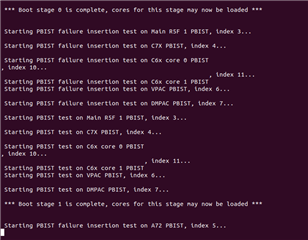

Ran PBIST for Stage 0

HwiP_Params_init complete

Primary core: Main R5F0-0: Requesting processor

Secondary core: Main R5F1-0: Requesting processor

Primary core: Putting in module and local reset the core Main R5F0-0

Secondary core: Putting in module and local reset the core Main R5F1-0

Primary core: Putting into Retention Main R5F0-0

Secondary core: Putting into Retention Main R5F1-0

Starting CSL_LBIST_enableIsolation

Starting CSL_LBIST_reset

Starting CSL_LBIST_enabledRunBISTMode

Starting CSL_LBIST_start

Starting CSL_LBIST_isRunning

LBIST not running

Starting CSL_LBIST_getMISR

Starting CSL_LBIST_getExpectedMISR

Starting CSL_LBIST_clearRunBISTMode

Starting CSL_LBIST_stop

Starting CSL_LBIST_reset

Secondary core: Powering off Main R5F1-0

Primary core: Powering off Main R5F0-0

Disabling isolation

Primary core: Putting into Retention Main R5F0-0

Secondary core: Putting into Retention Main R5F1-0

Checking that LBIST is not running

Secondary core: Powering off Main R5F1-0

Primary core: Powering off Main R5F0-0

Primary core: Taking out of local reset the core Main R5F0-0

Secondary core: Taking out of local reset the core Main R5F1-0

Primary core: Releasing Main R5F0-0

Secondary core: Releasing Main R5F1-0

LBIST failed with MISR mismatch: Expected 0xad7f4501 got 0x31669786

LBIST functional test failed for 2

Ran LBIST for Stage 0

ESM Call back function called : instType 0x3, intType 0x1, grpChannel 0x8, index 0x6, intSrc 0x106

ESM Call back function called : instType 0x3, intType 0x1, grpChannel 0x8, index 0x6, intSrc 0x106

Ra

ESM Call back function called : instType 0x3, intType 0x1, grpChannel 0x8, index 0x6, intSrc 0x106

n PBIST for Stage 1

HwiP_Params_init complete

Primary core: Main R5F1-0: Requesting processor

Secondary core: Main R5F1-1: Requesting processor

Primary core: Putting in module and local reset the core Main R5F1-0

Secondary core: Putting in module and local reset the core Main R5F1-1

Primary core: Putting into Retention Main R5F1-0

Secondary core: Putting into Retention Main R5F1-1

Starting CSL_LBIST_enableIsolation

Starting CSL_LBIST_reset

Starting CSL_LBIST_enabledRunBISTMode

Starting CSL_LBIST_start

Starting CSL_LBIST_isRunning

LBIST not running

Starting CSL_LBIST_getMISR

Starting CSL_LBIST_getExpectedMISR

Starting CSL_LBIST_clearRunBISTMode

Starting CSL_LBIST_stop

Starting CSL_LBIST_reset

Secondary core: Powering off Main R5F1-1

Primary core: Powering off Main R5F1-0

Disabling isolation

Primary core: Putting into Retention Main R5F1-0

Secondary core: Putting into Retention Main R5F1-1

Checking that LBIST is not running

Secondary core: Powering off Main R5F1-1

Primary core: Powering off Main R5F1-0

Primary core: Taking out of local reset the core Main R5F1-0

Secondary core: Taking out of local reset the core Main R5F1-1

Primary core: Releasing Main R5F1-0

Secondary core: Releasing Main R5F1-1

LBIST failed with MISR mismatch: Expected 0xad7f4501 got 0x31669786

LBIST functional test failed for 3

Ran LBIST for Stage 1

Ran PBIST for Stage 2

HwiP_Params_init complete

Primary core: A72 core 0: Requesting processor

Secondary core: A72 core 1: Requesting processor

Putting into module reset Device number 0 Device Id 4

Primary core: Putting in module and local reset the core A72 core 0

Secondary core: Putting in module and local reset the core A72 core 1

Putting into Retention Device number 0 Device Id 4

Primary core: Putting into Retention A72 core 0

Secondary core: Putting into Retention A72 core 1

Starting CSL_LBIST_enableIsolation

Starting CSL_LBIST_reset

Starting CSL_LBIST_enabledRunBISTMode

Starting CSL_LBIST_start

Starting CSL_LBIST_isRunning

LBIST not running

Starting CSL_LBIST_getMISR

Starting CSL_LBIST_getExpectedMISR

Starting CSL_LBIST_clearRunBISTMode

Starting CSL_LBIST_stop

Starting CSL_LBIST_reset

Secondary core: Powering off A72 core 1

Primary core: Powering off A72 core 0

Powering off Device number 0 Device Id 4

Disabling isolation

Putting into Retention Device number 0 Device Id 4

Primary core: Putting into Retention A72 core 0

Secondary core: Putting into Retention A72 core 1

Checking that LBIST is not running

Secondary core: Powering off A72 core 1

Primary core: Powering off A72 core 0

Powering off Device number 0 Device Id 4

Primary core: Taking out of local reset the core A72 core 0

Secondary core: Taking out of local reset the core A72 core 1

Putting into module reset Device number 0 Device Id 4

Primary core: Releasing A72 core 0

Secondary core: Releasing A72 core 1

LBIST failed with MISR mismatch: Expected 0xdd5cd3b3 got 0x3358dd14

LBIST functional test failed for 7

Ran LBIST for Stage 2